PC용 CPU로는 최고의 트랜지스터 수의 Banias

Banias에 대해 발표한 아난드 찬드라 세커 부사장

Banias 비밀의 베일이 절반 벗겨졌다. Intel은 9월 10일부터 개최된 개발자 컨퍼런스 "Intel Developer Forum Conference Fall 2002 (IDF)"에서 Banias의 다이 (반도체 본체) 레이아웃과 아키텍처 개요를 밝혔다. 베일 뒤로 엿본 것은 예상을 크게 넘어선 아키텍처였다.

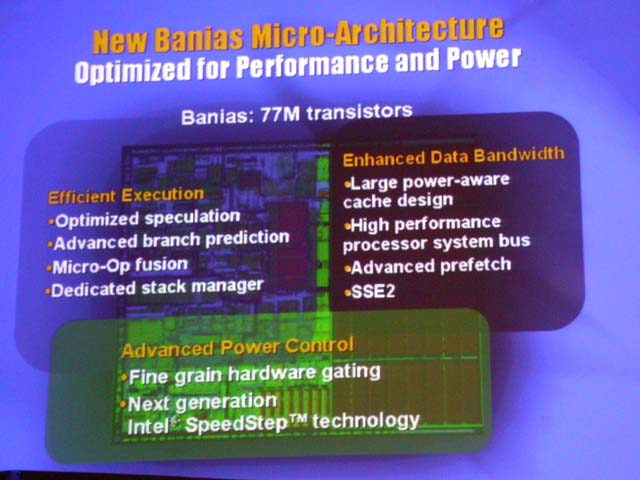

먼저 이번 최대의 놀라움 중 하나는 Banias의 트랜지스터 수이다. Banias의 트랜지스터 수는 7,700 만 트랜지스터. 이것은 0.13μm 판 Pentium 4 (Northwood : 노스우드)의 5,500 만 보다 많다. 사실 현재 데스크톱과 모바일 PC용 CPU로는 최고의 트랜지스터 수가 된다.

CPU의 소비 전력을 줄이고자 할 때, 통상이라면 트랜지스터 수를 줄여 물리적으로 소비하는 전력을 줄이는 것을 생각한다. 이것은 Transmeta의 Crusoe와 Centaur Technology / VIA Technologies의 C3를 보면 잘 알 수 있다. 양자는 아키텍처야말로 다르지만, 어느쪽도 트랜지스터 수를 Intel과 AMD의 CPU의 몇분의 1로 줄이고 저소비 전력을 달성했다.

하지만 Banias가 보여주고 있는 것은, Intel이 그러한 솔직한 접근 방식은 취하지 않았다는 것이다. 거의 CPU 마이크로 아키텍처 (내부 구조)의 개량정도로 데스크톱 CPU보다 훨씬 적은 전력을 달성하고 있는 것으로 보인다. 즉, Banias는 방대한 트랜지스터 수를 전력 효율적인 마이크로 아키텍처를 만드는 것에 쓰는 것으로, 모바일용으로 한다는 발상인것 같다.

이를 단순화하면 아래와 같은 구도가 된다.

통상의 모바일 CPU = 트랜지스터 수를 줄인다. → 저전력 & 저성능

Banias = 트랜지스터 수는 유지 → 트랜지스터를 성능 / 전력 효율의 향상에 쓰다 → 비교적 저소비 전력 & 고성능

즉, Banias는 모바일 아키텍처라고 말해도, 발상의 방향성이 (지금의 세대의) Crusoe와는 전혀 다른 것이다.

다이의 40%를 L2 캐시 SRAM이 차지한다.

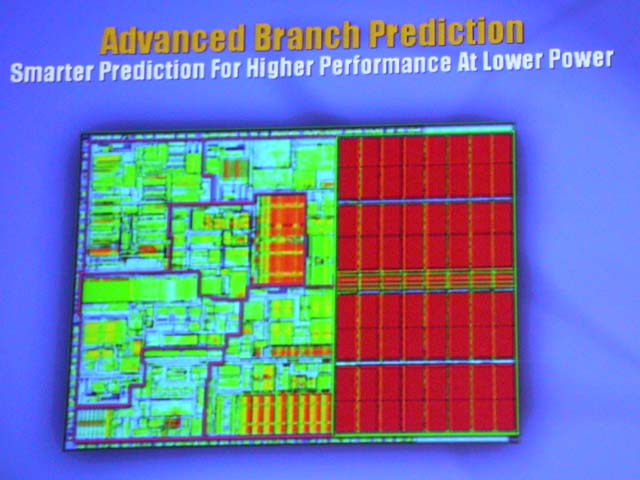

그러면 Banias의 트랜지스터 수와 다이를 확인해 가자. IDF에서 공개된 Banias의 다이 (반도체 본체) 레이아웃을 보면 상당 부분이 SRAM이 차지하고 있는 것을 알 수 있다. 개산에서는 다이 면적 중 약 40%가 L2 캐시가 차지하고 있다. 이전 칼럼에서 예상했던 것보다 L2 캐시 면적은 작지만, PC용 CPU로는 매우 크다. Banias는 1MB의 L2 캐시 SRAM을 탑재한다고 말해졌지만, SRAM의 면적을 보는한은, 그 정보는 옳은 것이다.

Intel의 CPU의 캐시 SRAM은 계산에서는 1 셀 6 트랜지스터의 구조라고 추측된다. 예를 들면, Northwood (5,500 만)는 Willamette (4,200 만)보다 1,300 만 트랜지스터가 늘며, L2 캐시는 256KB 늘었다. 256KB가 6 트랜지스터 SRAM라고 하면 트랜지스터 수는 약 1,250 만이 되기 때문에 앞뒤가 맞는다.

Banias 사양

Banias의 다이 레이아웃

Banias의 L2 캐시 SRAM도 동일한 셀 구조라고 하면, 1MB 캐시는 약 5,000 만 트랜지스터에서 Tag 등을 공제해도 CPU 코어의 로직 회로 + L1 캐시에 2,400 ~ 2,500 만 트랜지스터가 남는 것으로 추정된다. 한편, Pentium 4 계는 Northwood와 Willamette의 차이에서 역산하면 CPU 코어 로직 회로 + L1 캐시가 2,800 ~ 2,900 만 트랜지스터 정도로 추정된다.

| 명칭 |

총 트랜지스터 수 |

L2 SRAM |

CPU 코어 (+ L1) |

| Banias |

7700만 |

5000만 ? |

2400 ~ 2500만 |

| Northwood |

5500만 |

2900만 ? |

2800 ~ 2900만 |

매우 조잡한 계산하기 때문에 그다지 정확하다고는 말할 수 없지만, Banias의 로직 부분의 트랜지스터 수가 Pentium 4 계보다 적지만, 그렇게 극단적으로는 다르지 않은 것으로 추측 할 수 있다. 적어도 Pentium III 계 (L2 없는 Katmai가 950 만)보다 Banias 쪽이 훨씬 많은 것이 된다.

이것은 예상과 크게 다르다. 그것은 CPU에서 전력을 크게 소모하는 것은 논리 회로 부분이기 때문이다. 모바일용의 Banias는 당연히 Crusoe처럼 로직 부분의 트랜지스터 수를 줄일 것으로 예상하고 있었지만, 이것은 크게 빗나간 것이다. 논리 회로의 트랜지스터 수를 줄여 소비 전력을 낮추는 발상이 아님을 보이고 있다.

또한 다이 레이아웃에서 또 하나의 것을 알 수있다. 그것은 Banias의 다이 사이즈가 트랜지스터에 비해 작은 것이다. 눈대중으로는 Banias는 Pentium 4-M의 75% 정도의 다이 크기로 보인다. Banias는 다이 트랜지스터 밀도가 Intel CPU로서는 매우 높은 것이다.

보이는 Banias의 방향성

Banias는 로직 회로의 트랜지스터 수를 줄여 전력 소모를 낮추는 곧바른 발상의 모바일 CPU가 아니라는 것은 다양한 것을 의미한다. 우선 하나 명확한 것은 Banias도 어떤 의미에서 "성능 중시"의 CPU 인 것이다. 트랜지스터 수를 줄이면 그만큼 CPU 유닛 수나 특징을 깎아야 하고, 성능은 아무래도 깎인다. 하지만 Banias는 이만큼의 트랜지스터 수를 쓰는 이상 성능이 Intel의 주장하는 것처럼 높아도 놀라운 일이 아니다.

그리고 또 하나는 Banias의 포인트가 TDP (Thermal Design Power : 열 설계 전력)을 낮춘다기 보다, 동작시의 성능 / 전력 효율을 높이는 것에 있는 것이다. 정확하게 말하면, Banias의 경우 TDP는 Pentium III-M 수준을 유지하고 그 안에서의 성능 효율을 추구하고있는 것으로 생각된다. 트랜지스터 수가 이만큼 많으면 TDP를 낮추는 것은 상당히 어렵지만, 트랜지스터를 CPU의 실행 효율 향상에 지출함으로써 성능 / 전력 효율을 높일 수있게 된다.

실제로 이번 밝혀진 Banias의 TDP는 아래대로, 거의 Pentium III-M 시대와 같다. 즉, Crusoe과 C3처럼 더 아래의 TDP는 노리지 않는다. (지금으로는).

| Banias의 TDP |

|

| 일반 전압 판 |

25W |

| 저전압 (LV)판 |

13W |

| 초 저전압 (ULV) 판 |

8W |

이러한 설계 사상 때문에 Banias의 진가는 아마도 동작시에 발휘된다. 이번 Banias의 성능은 명확히는 나오지 않았지만, IDF의 키 노트 스피치에서 MPEG4 비디오 인코딩을 7W로 실행하는 것을 시현해 보였다. 즉, Banias라면 ULV 판 조차 MPEG4 인코딩을 실제적 속도로 해내는 것이다. OEM에 따르면, Intel은 Banias 1.6GHz의 배터리 구동시 성능이 Pentium 4-M 2.4GHz를 상회한다고 설명했는데, 이번 발표로, 이것도 진실성을 가지게 됐다.

그러면 Banias 마이크로 아키텍처는 성능 / 전력 효율을 향상시키기 위해 어떤 고안이 되어있는 것이다. 다음 칼럼에서 그 점을 보고하고 싶다.

2002년 9월 12일 기사 입니다.

[고전 2001.08.10] Banias의 샘플은 내년 여름, 발표는 2003 봄?

[고전 2001.08.29] 베니어스 2003년 상반기 출시 발표, 3.5Ghz 펜티엄4 데모

[고전 2000.08.25] 그래픽 통합 CPU 팀나(Timna)의 개요를 분명히-극적인 다이 크기 축소를 실현

[분석정보] 더 밝혀진 Yonah의 모습 확장된 C4스테이트

[고전 2003.02.20] Pentium M 1.60GHz의 처리 능력

[고전 2002.09.11] 이것이 Banias 플랫폼이다 CPU마이크로 아키텍처 편

'벤치리뷰·뉴스·정보 > 고전 스페셜 정보' 카테고리의 다른 글

| [고전 2002.11.14]Pentium 4 3.06GHz 빠른 리뷰 Hyper-Threading의 효과는 얼마나? (0) | 2005.10.11 |

|---|---|

| [고전 2002.10.04] Pentium 8 후보 Nehalem 아키텍처 (0) | 2005.10.10 |

| [고전 2002.09.27] 밝혀진 차세대 직렬 버스 "PCI Express" 사양 (0) | 2005.10.09 |

| [고전 2002.09.19] Intel, 3 차원 구조의 "트라이 게이트 트랜지스터 ' 발표 (0) | 2005.10.09 |

| [고전 2002.09.12] Hyper-Threading Technology를 지원하는 HTT Pentium 4 3.06GHz (0) | 2005.10.09 |

| [고전 2002.09.11] 이것이 Banias 플랫폼이다 CPU 마이크로 아키텍처 편 (0) | 2005.10.09 |

| [고전 2002.09.10] Intel Developer Forum Conference Fall 2002 기조 강연 리포트 (0) | 2005.10.09 |

| [고전 2002/07/09] Intel, McKinley Itanium 2의 출하를 개시 (0) | 2005.10.07 |