Intel의 CPU 설계 센터에 새롭게 더해진 방갈로르

지난 주 샌프란시스코에서 개최 된 ISSCC에서 Intel 6 코어 Xeon 제품군인 "Xeon 7400 시리즈 (Dunnington)" 회로 설계의 세부 사항을 발표했다. Dunnington은 MP 서버 전용의 하이 엔드 CPU이다. ISSCC에서 발표를 한 Intel의 Ravishankar Kuppuswamy 씨는 Dunnington는 인도의 Bangalore (방갈로르)에 있는 Intel의 설계 센터가 완성시킨 CPU임을 자랑스럽게 발표했다. Intel에 있어서 새로운 x86 CPU 설계 센터가 태어난 것이다.

Dunnington의 개요

Intel의 PC & 서버 전용 CPU는 몇개의 개발 거점에서 설계되고 있다. 첫째, Digital Enterprise Group의 미국 오리건 주 힐스보로 (Hillsboro)의 개발 센터에서 Pentium III / 4 및 Core i7 등을 개발하고 있다. 힐스보로와 함께 중요한 것은, Mobility Group에 속하는 이스라엘의 하이파 (Haifa)의 개발 센터로 Pentium M이나 Core 2, Sandy Bridge (샌디 브릿지) 등을 개발하고 있다.

이 밖에 미국 텍사스 주 오스틴의 개발 센터가 Atom 계 CPU 제품군을 설계하고 미국 캘리포니아 산타 클라라 (Santa Clara)는 초기 x86 CPU 및 IA-64 CPU와 서버 CPU의 파생품을 설계했다. 또한 미국 콜로라도 포트 콜린스 (Fort Collins) 디자인 센터는 IA-64 CPU를, 미국 캘리포니아 폴솜 (Folsom)은 칩셋과 CPU의 일부를 설계하고 있다. 사실, 각 개발 센터는 어느 정도 협조하여 개발을 하고 있다. 예를 들어, Intel은 "Penryn (펜린)"에 대해서는"이스라엘과 미국 (폴솜)에서 협조하여 개발을 진행했다 "고 설명했다.

그러나 핵심인 새로운 마이크로 아키텍처의 개발을 담당하고 있는 센터는 제한된다. x86에서는 Core i7의 힐스보로와 Core 2의 하이파, 그리고 Atom의 오스틴 3 센터다. Intel은 끊임없는 경쟁에 이기기 위해 설계 센터를 육성하고 개발 거점을 늘리고 있다. 방갈로르는 가장 새로운 사례로 다음 핵심거점의 후보로 있다.

Intel CPU 코어 수의 변천

파생 CPU 설계에서 CPU 마이크로 아키텍처의 개발 단계

이전 Intel의 Justin R. Rattner (저스틴 R · 래트너) 씨 (Intel Senior Fellow, Vice President, Director (Corporate Technology Group) and Intel CTO)에 인터뷰했을 때, 그는 Intel의 개발 센터의 육성 패턴을 다음과 같이 설명했다.

"새 CPU 개발 센터는 우선 메인 설계 센터에서 개발한 CPU 마이크로 아키텍처의 파생 제품을 개발하는 것부터 시작한다. 전형적인, 공정 이행 제품이나 모바일 용, 서버용의 파생 제품 개발을 담당한다. 이러한 파생 제품에서 1 ~ 2 세대 경험을 쌓고, 평가 받으면 신규 마이크로 아키텍처의 개발을 맡게된다. "

Rattner 씨는 이스라엘 디자인 센터가 이 패턴의 성공 사례라고 설명했다. 동 디자인 센터의 경우, MMX Pentium의 250nm 이행판으로 모바일을 메인 타겟으로 하는 "Tillamook (틸라무크)" 에서 설계를 시작했고, 취소 된 그래픽 통합 CPU "Timna (팀나)" 등을 다뤘다. 그리고 Pentium M (Banias : 베니어스)에서 Pentium III를 베이스로 하면서 거의 독자적 마이크로 아키텍쳐를 완성시켰다.

하이파의 패턴을 답습한다면, 방갈로르 설계 센터도 바로 육성 코스를 타고있는 셈이다. 평가 받으면 몇 세대 설계 후, 인도 출생의 마이크로 아키텍처가 등장하게 될 것이다. 그러나 하이파 센터처럼 이 과정으로 타고가는 것은 쉬운 일이 아니다.

예를 들어, Intel 486 세대까지는 일본에서도 파생 제품의 설계를 행하고 있었다. 이스라엘과 마찬가지로, 쓰쿠바 디자인 센터는 육성 코스를 걷기 시작한 유력 후보 중 하나였다. 그러나 이미 설명했듯이, MMX Pentium 세대로는 파생 상품의 개발은 이스라엘 하이파가 담당하게 되고, 일본에서의 개발은 종식됐다. 원인은 모르겠지만, 여기에서 코스가 다르게 갔다면, 지금쯤 일본 설계의 Intel CPU가 세계를 석권하고 있었을지도 모른다.

실패한 Whitefield 뒤에 Dunnington을 맡아

Intel이 인도에 개발 센터를 개설한 것은 자연스러운 흐름이었다. 왜냐하면 CPU 관련 엔지니어는 원래 인도계가 많기 때문이다. 어느 CPU 업계 관계자는 "실험실에서 돌을 던지면 인도계 또는 중국계에 맞는다."라고 말했다. 실제로 2002년에 Intel은 방갈로르에 R & D 센터를 설립한 당초는 미국 Intel에서 인재가 U 턴 했다고 말했었다. 그리고 이 센터의 첫 작품이 Dunnington 이었던 셈이다.

그러나, Intel 방갈로르 디자인 센터에게 Dunnington은 사실 첫 번째 CPU 개발 경험이 아니다. Dunnington 전에 이 센터는 Core MA의 네이티브 쿼드 코어 CPU "Whitefield (화이트 필드)"를 개발하고 있었지만, 거기에서 실패를 하고 말았다.

Whitefield는 쿼드 코어 IA-64 계의 "Tukwila (투킬라)"와 "공통 플랫폼 (Common Platform)"이 될 예정이었다. 공통 플랫폼 구상은 당초 IA-32의 MP 서버 CPU와 IA-64 CPU 양 계통의 공통 CPU 소켓이 계획되어 있었다. 따라서 일반적인 칩 상호 연결로 "QuickPath Interconnect (QPI)" (원래는 'CSI : Coherent Scalable Interface"라고 했다)를 사용할 예정이었다. Whitefield가 완성 됐으면, QPI를 구현한 첫 CPU가 되는 것이다. 2006년 이후에 투입될 계획이 있었다 (QPI는 네할렘에서 쓰죠. QPI는 CPU와 노스브릿지를 연결하기도 하지만, CPU와 CPU를 연결하는 버스이기도 합니다. 다수의 CPU를 탑재하는 서버에서는 반드시 있어야죠. QPI가 도입된 이후 모든 고성능 서버용 CPU는 QPI 탑재. 이걸 아이테니엄과 똑같이 통일하면, 각각의 서버 CPU 설계에서 버스 부분은 일을 줄일 수 있는 것이고, 공통 칩셋을 쓸 수도 있게 되는 거죠. 뭐 나중에는 노스브릿지도 CPU에 통합이 되지만, 어쨌든 간에요.).

그러나 Whitefield의 개발은 취소되었다. Justin R. Rattner는 2006년 봄에 그 경위를 다음과 같이 설명했다.

"설계팀 성장에는 약 8년이 걸린다. 단순히 칩 엔지니어를 모은 것만으로는 좋은 디자인 팀이 될수 없다. Intel의 경우에는 잘되지 않았던 예가 인도였다. 인도는 쿼드 코어 CPU를 설계 하고 있었지만, 지연이 계속됐다. 따라서 결국 완성 할 수 없다고 판단하여 중단한 문제의 하나는 정보의 공유가 잘되지 않았던 것이다. 예를 들어, 1 명이 만든 RTL (Register Transfer Level) 파일을 다른 엔지니어가 제대로 이해하고 협력하지 않으면 설계가 진행되지 않는다. 인도 엔지니어 간의 연계가 잘되지 않고, 개발이 난항을 겪고 말았다. "

Whitefield에 비하면 얌전한 Dunnington의 설계

Whitefield의 개발 취소는 인도의 미디어에서는 크게 보도되었다. ( "Intel decides not to develop Whitefield chip"The Times of India, 2005/10/27). 전후하여 방갈로르의 간부가 Intel을 그만 둔 것 등도 보도되었다.

그리고 Whitefield 취소 후, Intel의 서버 CPU 로드맵에 등장한 것이 Dunnington이었다. 정확하게는 네이티브 쿼드 코어의 Whitefield가 무산된 것으로, 급거 듀얼 다이 쿼드 코어 CPU "Tigerton (타이거톤)"이 투입되었다. Tigerton은 기존의 듀얼 코어 CPU를 이용하여 CPU의 엔지니어링는 최소한으로 억제하고, 칩셋을 궁리하는 것으로 단기간에 쿼드 코어를 실현한 대타였다. 그리고 Tigerton의 후계로서 네이티브 6 코어의 Dunnington이 놓이고 Bangalore 팀이 다시 도전하게 되었다.

Whitefield는 네이티브 쿼드 코어 CPU로 캐시 계층 구조를 최적화, QPI와 메모리 인터페이스를 통합한다고 볼 수 있었다. 그렇다면 Core MA의 쿼드 코어화를 행할 뿐만 아니라 Nehalem 같은 인터페이스 부분을 개혁하는 CPU를 개발하고 있던 것이된다. Whitefield의 개발이 지연되고 결국 취소되어 버린 원인은 이 부분에 있었을지도 모른다. 새로운 요소가 많은 대규모 설계에서 설계자 간의 커뮤니케이션이 잘 잡히지 않고, 모듈 간의 설계의 일관성이 없게 된지도 모른다.

그래서인지 Dunnington은 Whitefield 보다 훨씬 얌전한 설계로 되어있다. 기본적인 구성은 듀얼 코어 Penryn을 3 세트 올리고 16MB의 대용량 L3 캐시를 탑재, 코어 및 버스의 조정을 행하는 스위치 로직을 구현했다. Penryn 코어는 대부분 변경한 흔적이 보이지 않고, 메모리 인터페이스의 통합이 아니라 FSB (Front Side Bus)도 기존 병렬 버스 인 채로, QPI의 도입은 Nehalem 계까지 보류되었다. 즉, 새로운 기술 요소를 줄이고 새로운 설계의 규모를 억제하고, 신속한 개발을 목표로 한 것이 Dunnington 이라고 할 수 있겠다.

실제로 2005년의 Whitefield 취소에서 2008년 Dunnington의 투입까지의 시간 차이는 불과 3년. 이것은 Dunnington의 실제 설계에 걸린 시간은 2년 정도 였다는 것을 보여주고있다. CPU 개발로서는 상당히 짧은 기간이다. (CPU 코어의 아키텍처를 새로 만든게 아닌 펜린(45나노 콘로)을 그대로 가져다 쓰면서도 언코어 부분의 설계와 전체 배치에 이렇게 걸렸다는 거죠.)

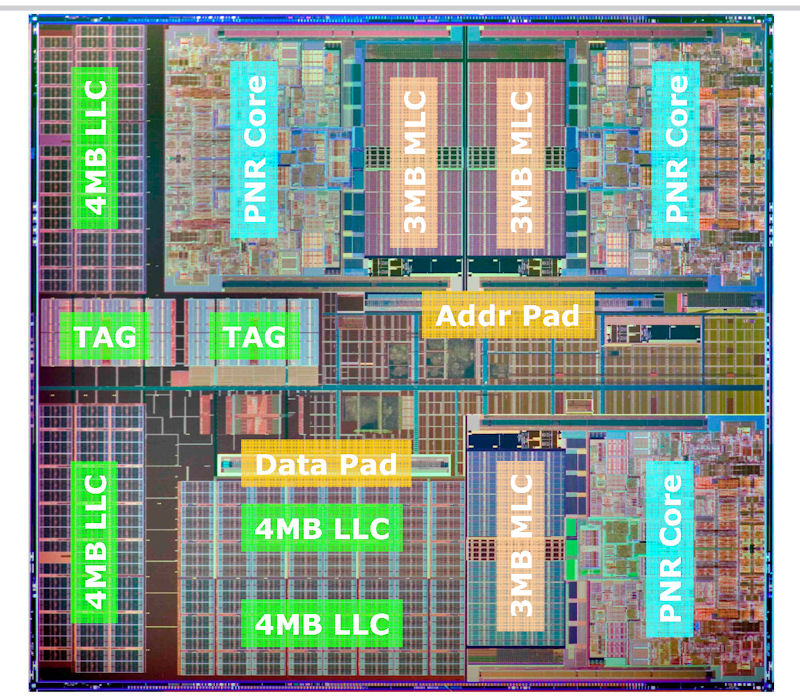

Penryn 기반의 듀얼 코어 단위로 제어

ISSCC에서 발표 내용을 봐도, Dunnington에는 Penryn (데스크탑 울프데일) 기반으로 한 부분을 볼 수있다. 예를 들어, Dunnington은 다이 (반도체 본체)에 결함이있는 경우 결함을 포함하는 모듈을 무효화 해 부분적인 굿 다이 (양품)로 제공 할 수 있도록 하고 있다. 이 메커니즘 자체는 Dunnington의 후계가 되는 8코어의 Nehalem-EX와 같지만, 입도가 다르다.

Nehalem-EX는 CPU 코어마다 활성화 / 비활성화 할 수 있다. 대조적으로, Dunnington에서는 페어가 된 듀얼 CPU 코어 단위로 활성화 / 비활성화 제어를 행하고있는 것 같다. 보다 진화한 Nehalem-EX는 개별 CPU 코어 단위로 제어를 행하고 있는 부분이 Dunnington에서는 근원인 Penryn이 듀얼 코어 모듈 기반이다.

덧붙여서, 16MB의 L3는 4MB 씩 4개의 지역 단위로 제어되고 있다. Dunnington의 정품 SKU (Stock Keeping Unit = 상품)에서 CPU 코어 수가 6과 4의 2종류의 바리에이션, L3 캐시 크기가 16MB, 12MB, 8MB의 3종류의 바리에이션인 이유가 이것으로 알 수 있다.

16MB의 L3 캐시는 0.3816 제곱 μm의 셀 크기로 4MB 단위의 블록으로 나뉘어져 있다. 태그 캐시 어레이는 1.5MB로 0.54 제곱 μm. 캐시는 1MB 당 16의 서브 어레이로 구성되어 있다. 서브 어레이의 크기는 Nehalem-EX와 동일 캐시 액세스 할 때 해당 주소를 포함 서브 어레이 만이 파워업된다. L3 캐시 전체의 대부분은 잠을 잘 수 있기 때문에 누설 전류를 억제 할 수 있다.

Dunnington 코어

Nehalem 계 보다 트랜지스터적으로 전력 절약 Dunnington

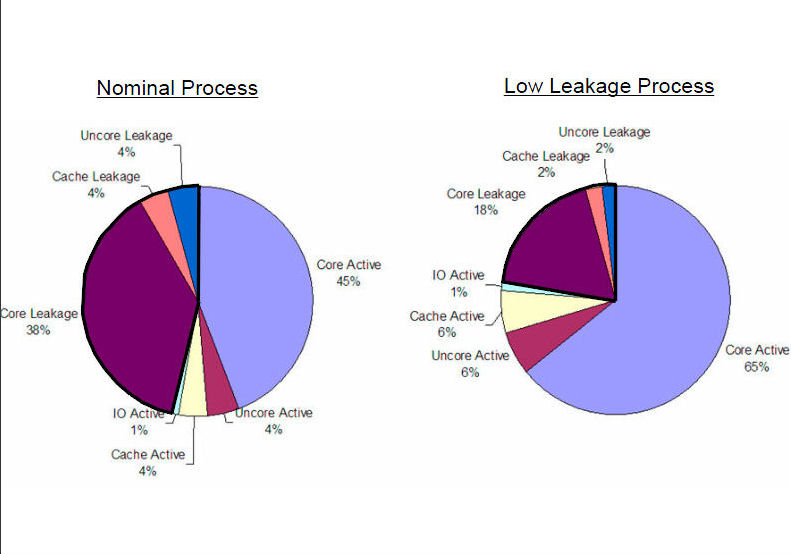

Intel은 현재 CPU 회로 설계에서 채널 길이가 다른 트랜지스터를 구사하고 있다. 요주의 경로는 고속화를 위해 채널 길이가 짧고 고속이지만 리크 전류가 다소 많은 트랜지스터를 사용한다. 중요하지 않은 부분은 채널 길이가 길고 저속이지만 리크 전류가 작은 "Long Le" 트랜지스터를 사용한다.

Dunnington의 경우 CPU 코어의 트랜지스터 65%와 언 코어 (CPU 코어 이외의) 부분의 90%가 Long Le 타입의 절전 트랜지스터 되어 있다고 한다. 재미있는 것은, Nehalem 계열의 Nehalem-EX는 CPU 코어의 58%와 언 코어 부분의 85%가 Long Le 타입이다. 즉, 동일한 45nm에도 Penryn 계보다 Nehalem 계가 빠른 트랜지스터의 비율이 많다. 언 코어 부분은 Nehalem 계가 고속 I / O를 사용하고 있기 때문에라고 추측된다. CPU 코어 내용은 Nehalem 계는 아직 여유를 갖게 한 설계를 하고 있는지도 모른다.

이러한 사정으로, Dunnington의 것이 공정 기술에 의한 절전 효과가 클 것으로 추측된다. 그러나 Nehalem 계는 CPU 코어의 파워 게이팅 하면 절전 모드의 CPU 코어 전압을 크게 낮추고, 누설 전류 (Leakage)를 억제되기 때문에 정말 절전 여부는 응용 프로그램과 이에 따르는 CPU 부하에 따라 상당히 다른 것이다. 그러나 Dunnington에서는 트랜지스터의 튜닝의 효과가 큰 것은 확실하다.

Intel은 Dunnington의 대부분을 고속 트랜지스터로 만든 경우에는 TDP가 200W를 초과 할 것으로 예측된다. 그러나 현재와 같이 저전력 트랜지스터를 높은 비율로 혼합한 경우에는 TDP를 160W까지 낮출 수 있다. 또한 주파수를 13% 떨어 뜨리는 것으로 (Dunnington는 최대 2.66GHz), 130W 이하의 TDP를 실현할 수 있었다고 말한다. 누설 전류 (Leakage)도 65nm 공정의 경우와 마찬가지로 Long Le의 사용으로 1 / 3로 줄일 수 있었다고 한다. Dunnington 6 코어 버전의 최저 TDP는 65W로 1CPU 코어 당 TDP는 11W 평균으로 억제된 것이다.

최근 Intel CPU의 패턴에서는 최초로 투입되는 데스크탑 및 모바일 용 상품에 1 페이즈 늦게 등장하는 하이 엔드 멀티 코어 버전에서 대규모 CPU에 필요한 전력 절약 화 등이 발달하게 된다. 그리고 그 기술이 다음 페이즈의 데스크톱 및 모바일 버전에도 반영된다는 패턴이 있는 것으로 보인다.

그런 의미에서 Dunnington은 온당한 제작으로 보인다. 그러나 Whitefield에서 의도한 것 같은 혁신성이 강한 디자인이 아니다. 이것이 Intel 내부에서 어떻게 평가되는지 모르겠다. 따라서 방갈로르 Intel의 설계 센터가 앞으로 어떤 역할을 짊어지고 갈 것인가는 미지수다.

Dunnington의 블록 다이어그램

트랜지스터의 누설 전류의 변화

2009년 2월 24일 기사 입니다.

[분석정보] Intel 래트너 CTO에게 듣는 Atom 탄생 비화

[분석정보] 아이테니엄(Itanium)을 둘러싼 불안과 기대

[정보분석] 같은 무렵에 시작된 Nehalem과 Larrabee와 Atom

[정보분석] 2개의 CPU 개발팀이 경쟁하는 Intel의 사내 전략

[정보분석] Intel 힐스보로가 개발하는 CPU 아키텍처의 방향성

[분석정보] 5W 이하의 저전력 프로세서의 개발로 향하는 Intel

[고전 1998.11.4] DEC의 Alpha 개발 팀이 대 Intel 진영에

[정보분석] Merom(메롬) 이후인 Nehalem(네할렘) 과 Gilo(길로)

[정보분석] 2년 주기로 아키텍처를 쇄신하는 Intel

[고전 2000.2.25] 인텔 사내경합이 낳은 Willamette 1.4GHz

[정보분석] 인텔의 2013년 CPU 하스웰로 이어지는 네할렘 개발 이야기

[고전 2000.08.25] 그래픽 통합 CPU 팀나(Timna)의 개요를 분명히-극적인 다이 크기 축소를 실현

[분석정보] ARM 코어의 다양한 라이센스 모델과 CPU코어의 설계 흐름

[고전 2005.03.03] Pat Gelsinger 부사장 기조 강연 리포트 새 로드맵과 코드 네임 다수 등장

[분석정보] 차세대 CPU Conroe의 내부 구성이 명확히

[분석정보] Intel의 개발 책임자에게 듣는, Skylake 개발 비화

'벤치리뷰·뉴스·정보 > 아키텍처·정보분석' 카테고리의 다른 글

| [분석정보](암달의 법칙) 2010년대 100 코어 CPU 시대를 향해서 달리는 CPU 제조사 (0) | 2009.05.13 |

|---|---|

| [분석정보] 인텔 GDC에서 라라비 명령 세트의 개요를 공개 (0) | 2009.03.30 |

| [분석정보] GDC 2009 드디어 소프트 개발자 정보도 나온 "Larrabee" (0) | 2009.03.28 |

| [분석정보] CPU 아키텍처 시대의 전환점이 되는 AMD의 "Bulldozer" (0) | 2009.03.18 |

| [분석정보] 그래픽 및 DirectX 로드맵을 정리 (0) | 2009.02.18 |

| [분석정보] Intel이 개요를 밝힌 옥타 코어 CPU Nehalem-EX (0) | 2009.02.12 |

| [분석정보] 그리고 CPU는 DRAM 다이도 통합 (0) | 2008.12.26 |

| [정보분석] Intel 힐스보로가 개발하는 CPU 아키텍처의 방향성 (0) | 2008.12.17 |