Intel이 FIVR (Fully Integrated Voltage Regulator)의 세부 사항을 공개

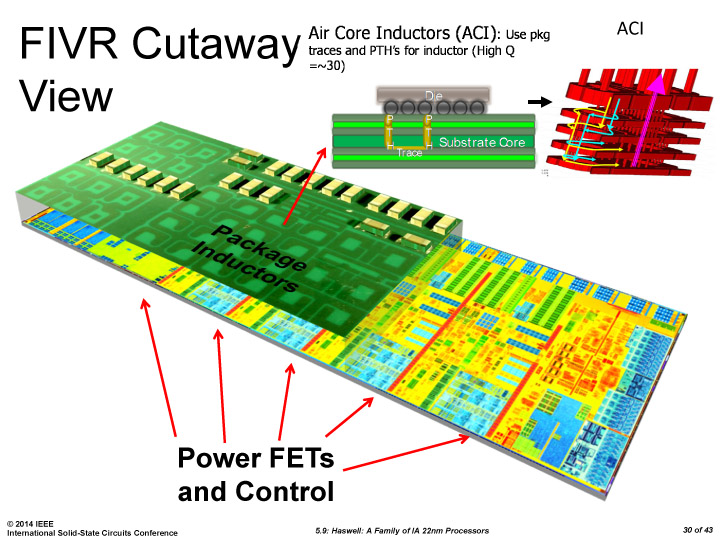

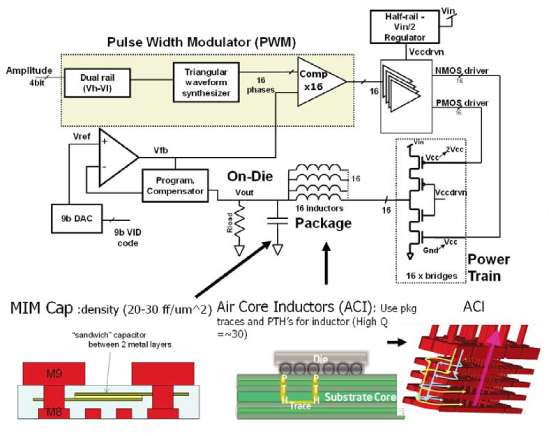

Intel은 "4세대 Intel Core 프로세서 (Haswell)"절전 기능의 열쇠인 통합 전압 레귤레이터 "FIVR (Fully Integrated Voltage Regulator)"의 개요를 점차 밝혔다. Haswell의 FIVR은 온다이 (On-Die)에 구현된 DC-DC 컨버터와 고밀도의 'MIM (metal-insulator-metal) 커패시터, 그것을 온 패키지 "패키지 트레이스 인덕터 (package trace inductor)"을 사용한다. FIVR 단위 중 인덕터 부분만 온다이가 아닌 패키지 측에있다. FIVR의 개요는 2014년 2 월의 반도체 기술 컨퍼런스 ISSCC (IEEE International Solid-State Circuits Conference)에서 공개되었다.

Intel이 FIVR에서 "전체 통합 (Fully Integrated)"을 강조하는 것은 지금까지도 CPU 패키지에 외장형 전압 레귤레이터 (VR)의 서브스트레이트를(substrate 칩의 기판, 반도체 패키지 기판. 보통 CPU라 부르는 물건의 반도체 다이를 제외한 부분.) 더해서 전력을 공급하는 솔루션이 존재했기 때문이다 . Intel은 이번에는 VR을 완전히 CPU 패키지에(패키지 자체에) 통합하기 때문에 Fully 부분을 더해 FIVR라고 부르고 있다. 다만 Intel의 FIVR은 아직 완전히 CPU의 다이에 모든 구성 요소를 통합한 것을 의미하지 않는다. 어디 까지나 패키지 수준의 통합으로, 온다이 통합을 실현할 때 Perfect IVR (PIVR) 같은 이름으로 올지도 모른다.

CPU를 위한 전압 조정기를 칩에 통합하는 데 가장 큰 문제가 되는 것은 큰 외부 부품인 인덕터의 통합이다. Intel은 이를 위한 기술 개발에 노력을 기울여왔다. Haswell의 FIVR는 그 성과이며, Intel의 독자 기술에 의해 거의 독주 (IBM이 보통주행) 하고 있다.

[분석정보] Intel의 "Ozette"칩에서 Haswell(하스웰)까지의 전압 레귤레이터 통합의 길

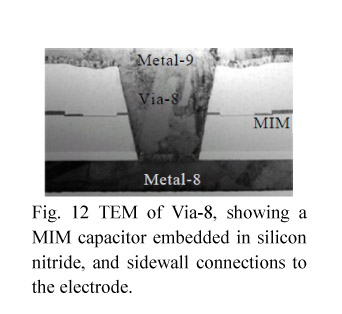

FIVR에 사용되는 22nm 공정의 MIM 커패시터 기술은 Intel은 2012년 6월과 2013년 6월의 "VLSI Symposium (Symposium on VLSI Technology and Circuits) "에서 발표되고있다. MIM 커패시터를 Intel 22nm 공정의 배선층 상단의 M9와 M8 사이에 생성한다. 매우 전류 밀도 높은 캐패시터를 소면적에 실장이 가능하도록 되어 있다.

VLSI Symposium에서 발표된 슬라이드

온다이 컨버터와 MIM 커패시터 내용은 지금까지 기술이 밝혀지고 있었다. 그러나 패키지 측에 올린 인덕터 내용의 개요는 밝혀지지 않았다. Intel은 ISSCC의 타이밍에 FIVR의 개요를 발표한 것은 올해 (2014년) 3월에 FIVR 세부 정보를 학회 (APEC : Applied Power Electronics Conference)에서 발표할 예정이기 때문으로 추측된다. ISSCC에서 공개된 정보의 대부분은 이전에 APEC 세션 개요에서 밝히고 있다.

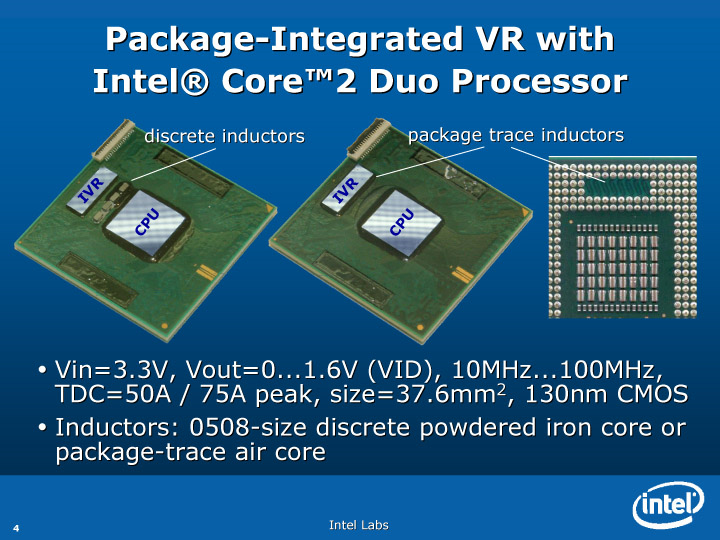

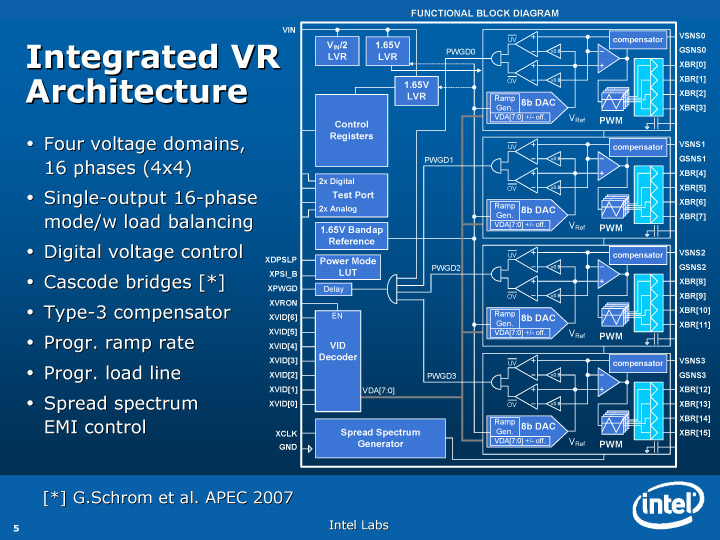

Haswell에 사용된 기술은 Core 2 Duo 기반의 테스트 칩의 발전

Haswell에서 Intel이 사용한 캐패시터 기술 "패키지 트레이스 인덕터 (Package Trace Inductor) "로 CPU의 패키지 서브 스트레이트에 에어 코어 인덕터 (Air Core Inductor : 공심 인덕터)를 생성하는 것. 따라서 메인 보드의 CPU 측에도 칩 패키지에도 외부 어레이 커패시터를 배치 할 필요가 없다. 대신 칩 패키지 내에서 CPU를 올리는 서브스트레이트에 일정한 크기의 인덕터 패턴이 배치된다.

Intel은 이 기술에 대해서는 과거 Core 2 Duo를 사용한 테스트 패키지를 공개했다. 아래의 슬라이드 사진이 테스트 칩으로 왼쪽의 사진에서는 CPU와 전압 레귤레이터의 실리콘 칩 사이에 외부 인덕터가 오른쪽 사진에서는 VR 실리콘 아래에 패키지 트레이스 인덕터가 생성되어 있다.

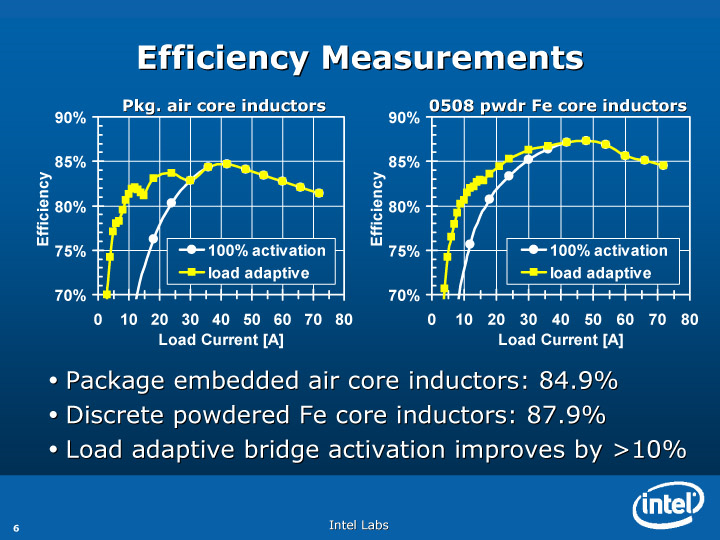

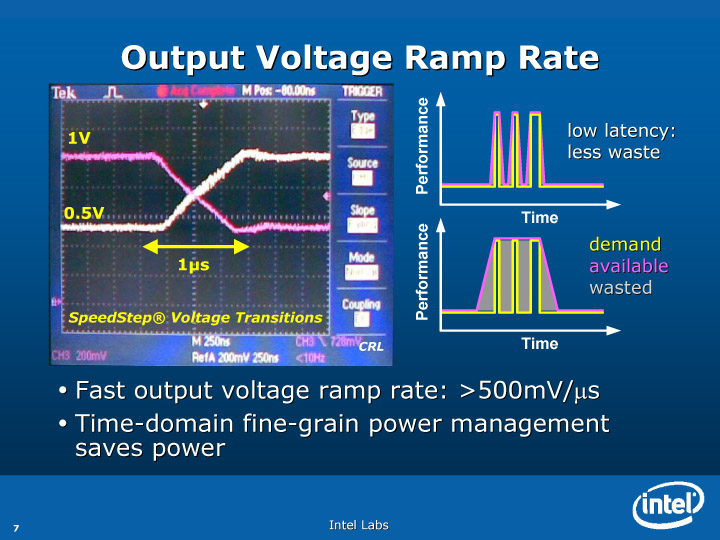

이때 테스트 칩은 단순히 외부 VR을 전제로 한 Core 2에 연결하는 것이었다. VR 자체는 여전히 CPU에 통합되지 않았다. 그러나 스위칭 주파수는 60MHz 빠르고, 인덕터의 효율은 84.9 %로 외부와 거의 손색이없고, 전압 램프도 0.5V에서 1V에서 1us (마이크로 초)로 좋은 스펙이었다.

또한 Intel은 패키지 서브스트레이트의 도체 층에 구현하는 패키지 트레이스 인덕터 관련 특허 (US Patent 8,368,501)를 보유하고 있다. 패키지 트레이스 인덕터의 과제는 CPU에 공급하기에 충분한 전류량이 어려운 것으로, 서브스트레이트 상에서 큰 면적을 가질 것이라고 한다. 대조적으로, Intel은 좁은 서브스트레이트 면적에 구현 가능하고, 큰 전력을 공급하면서 EMI를 억제 할 수있는 패키지 트레이스 인덕터 설계 특허를 취득했다. 특허 출원은 2006년으로 되어있다. 그러나 이 기술이 Haswell과 관련이 있는지 여부는 아직 모른다.

서브스트레이트에 인덕터를 생성한 Haswell

ISSCC는 Haswell의 FIVR 기술에 대해 Intel은 아래의 슬라이드를 보여 주었다. Haswell의 패키지 서브스트레이트에 인덕터 패턴이 생성된 이미지이다. 서브스트레이트의 PTH (Plated Through-Hole)와 트레이스 (Trace)를 사용해 에어 코어 인덕터 (Air Core Inductor : ACI)를 만든다. PTH의 방향을 도는 코일 모양으로 되어 있는 것으로 보인다. 비자성 재료의 트레이스이기 때문에 표준적인 패키지 기술로 제조된다 Intel은 설명한다. 스위칭 VR은 16 페이즈의 다른 전압을 지원하는 사양이어서 인덕터 부분도 대응한 구성이다.

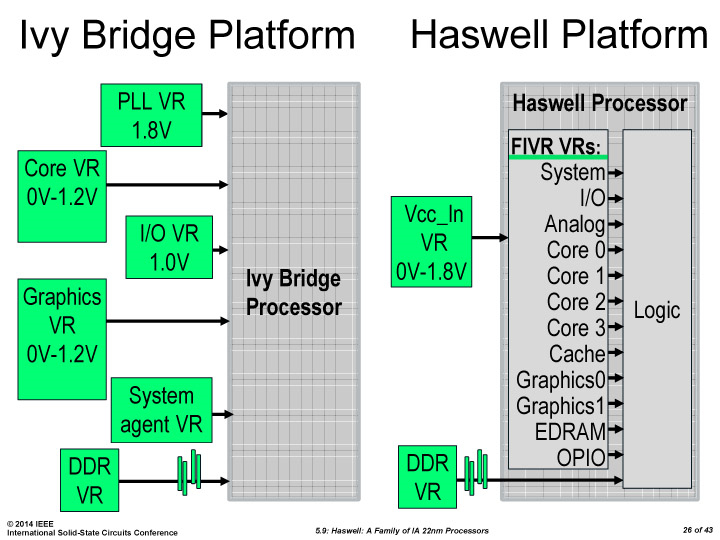

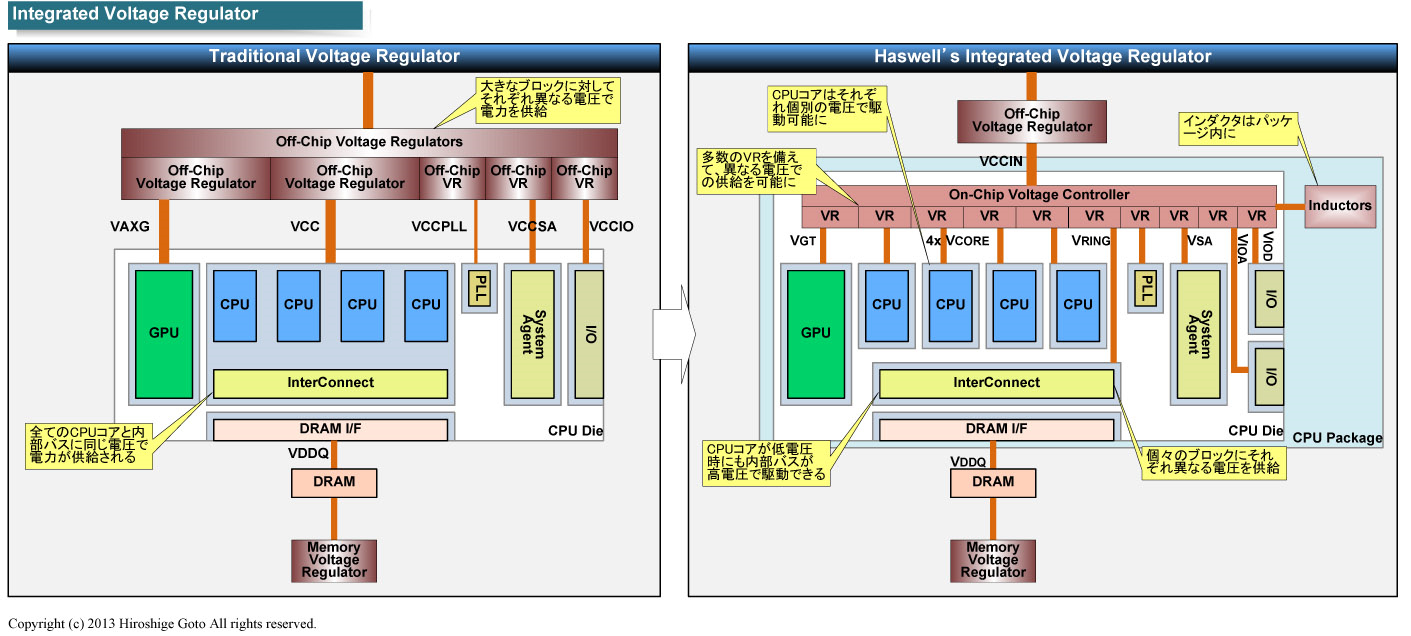

기존의 Intel CPU 에서는 오프 칩 마더 보드 상의 전압 레귤레이터 (VR)에서 CPU의 각 유닛에 대해 전력이 다른 전압 레일에서 공급되고 있었다. 그것에 비해, Haswell에서는 FIVR에서 각 장치에 대해 서로 다른 전압 레일로 공급된다. 오프 칩 VR에서 Haswell에는 VccIN에 단일 레일로 전력 공급되고, Haswell 온칩 FIVR에서 변압이 되어 각 유닛에 공급된다.

Ivy Bridge는 (CPU 외부의 마더보드)VR에서 6개의 레일로 전력을 공급하고 있었다. Haswell에서는 외부에서 레일 VccIN 외에는 DRAM과 DRAM 인터페이스에 공통되는 DDR VR 뿐이다. 그리고 CPU의 각 유닛으로의 전압 레일은 유닛마다 미세 입도화 되었다. 기존의 Intel CPU에도 각 CPU 코어는 부하에 따라 전압과 동작 주파수를 바꾸는 "DVFS (Dynamic Voltage and Frequency Scaling)"을 행하고 있었지만, CPU 코어 블록 전체에 공급하는 전압은 공통이었다. 따라서 DVFS의 본래의 강한 맛은 활용되지 못했다.

그것에 비해, Haswell 에서는 CPU 코어 각각이 별도의 전압으로 동작하게 되었을뿐 아니라 지금까지 CPU 코어와 동일한 전압이었던 캐시 / 링 버스도 분리되고, GPU 코어도 최대 2계통의 레일로 분할됐다. 각 코어 유닛에 최적의 전압을 공급하여 불필요한 전력 소비를 억제하고 최적화 할 수 있게 되었다. Haswell은 eDRAM 버전은 eDRAM 칩의 전력과 eDRAM의 인터페이스 OPIO의 전력 레일도 가지고 있기 때문에 최대 13 레일 FIVR을 갖춘다고 말한다.

Haswell의 FIVR

140MHz 고속 전압 스위칭 주파수

이러한 레일 중 CPU 코어와 GPU 코어에 대한 것은 DVFS를 위해 전압 스위치를 지원해야 한다. Haswell에서는 VR을 칩에 통합한 것으로, 극적으로 전압 스위치의 속도가 빨라졌다. 스위칭 주파수는 140MHz로 매우 빠르다. 슬립에서 벗어날 때 0V에서 0.8V의 실제 승압 시간은 320ns (나노초). 또한 터보 모드로 0.8V에서 1.05V로 승압하는 경우도 약 100ns로 고속이다.

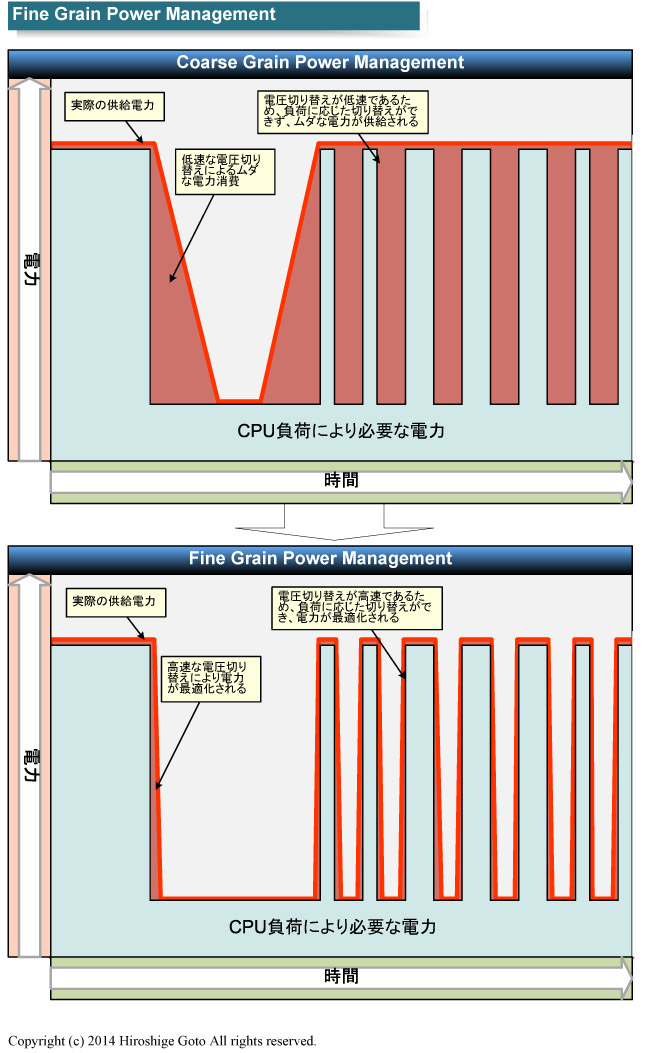

140MHz라는 스위칭 주파수는 통상의 오프 칩(메인보드에 있는) VRM이 수 100KHz ~ 수 MHz 인 것과 비교하면 꽤나 고속이다. 이전의 패키지 트레이스 인덕터의 테스트 칩과 비교해도 스펙은 상기의 테스트 칩은 0.5V에서 1V까지 승압 1,000 ns (1us)라는 사양이었다. 전압 램프 레이트는 테스트 칩이 500mV/us였던 것에 비해, Haswell에서는 2,500 mV / us 로 5배 빠르다. 기존의 VR에 비해 극적으로 전압 변환이 고속으로 되기 때문에,지금까지라면 전압 스위칭 속도의 제약으로 인해 일정한 전압으로 연속 구동되는 등의 경우에도 미세 전압을 강압할 수 있게된다. 아래의 차트는 Intel의 차트를 알기 쉽게 정리한 것이다.

Fine Grain Power Management의 설명

그림의 가로축은 시간, 세로축은 전력을 보여준다. CPU의 부하에 의한 전력 수요는 하늘색으로 표시되어있다. 위 차트는 기존의 오프 칩 VRM에 의한 저밀도 입도 (Coarse Grain)의 전압 스위칭이기 때문에 전환에 시간이 걸린다. 따라서 전압 전환시 낭비가 발생하고 있으며, 오른쪽의 간헐적인 부하에서는 일정 전압으로 실행할 밖에 없기 때문에 엄청난 낭비가 발생한다. 그것은 아래의 통합 전압 레귤레이터에 의한 세밀한 제어가 되면 부하에 따른 전압 제어되고, 전력의 낭비는 거의 생기지 않게된다. 이것이 Haswell에서 실현 될 수 있었던 것이다.

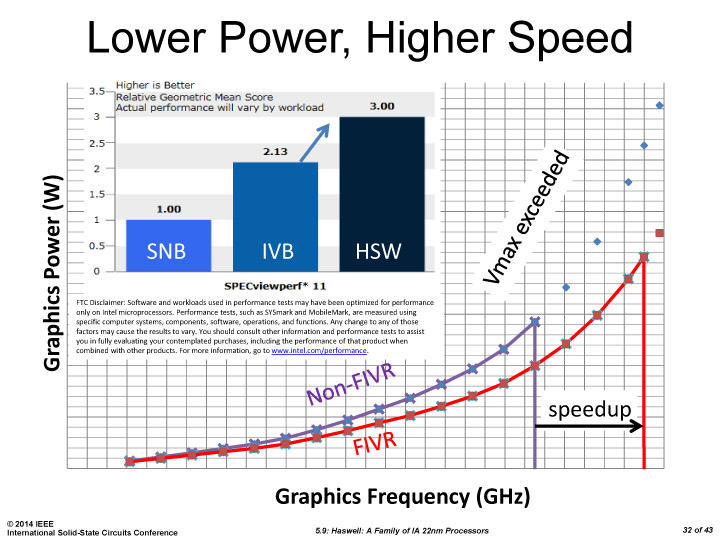

ISSCC에서는 FIVR의 이익으로 Haswell에서는 절전력화 되었을 뿐만 아니라, 스립에서 탈출시의 응답성도 크게 향상됐다고 강조했다. 이것은 노트북 PC에서 Haswell의 장점으로 잘 알려져 있는 포인트다. 또한 특히 GPU 코어는 FIVR의 이익으로 상당한 속도도 실현할 수 있었다고 설명했다. 연속 작동하고 있는 것으로 보이는 GPU 코어도 FIVR 의한 전압 제어의 미세 입도가 효과를 발휘하는 것을 알 수있다.

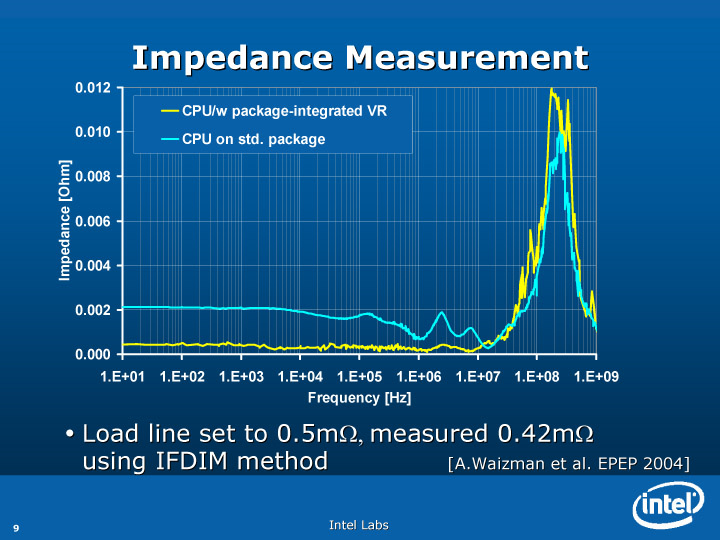

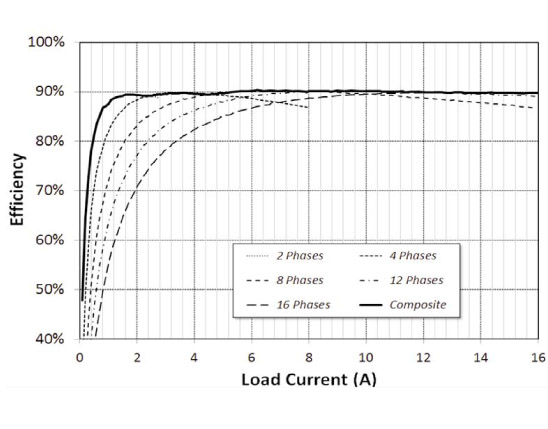

ISSCC는 Haswell의 FIVR 에서는 Unity Gain Bandwidth (UGB)이 80MHz에 도달, 전류 밀도도 32A / 제곱 mm로 고밀도인 것이 밝혀졌다. 다이 비용면에도 저비용으로, 패키지 측도 특별한 재료가 필요 없기 때문에 상대적으로 저비용으로 생산할 수 있다는 것이다. 풀로드시의 컨포지트 효율도 90%를 유지한다.

Intel의 FIVR 관련의 지금까지의 발표는 서버에 포커스

Intel의 FIVR는 칩의 절전력성을 높이고 배터리 구동시간을 연장할 뿐만 아니라 코어의 액티브시 전력 최적화로 다크 실리콘 (전력이 저감될 수 없기 때문에 다이에서 켜지 않는 지역이 증가 하는) 문제도 줄일 수 있다. 슬립에서 복귀도 빠르게 할 수 있기 때문에 모바일 분야에서도 이점이 많다.

Intel의 절전력 기술 중에서 다른 제조업체들에게 가장 골치거리인 무기는 이 FIVR이다. IBM 이외에는 타사의 대부분이 지금에는 따라갈수 없기 때문이다. 다만 AMD는 "통합 전압 레귤레이터는 업계 전체의 흐름으로, 시기가 오면 대응한다"(Mark Papermaster 씨 Senior Vice President and Chief Technology Officer, AMD) 라고 설명했다.

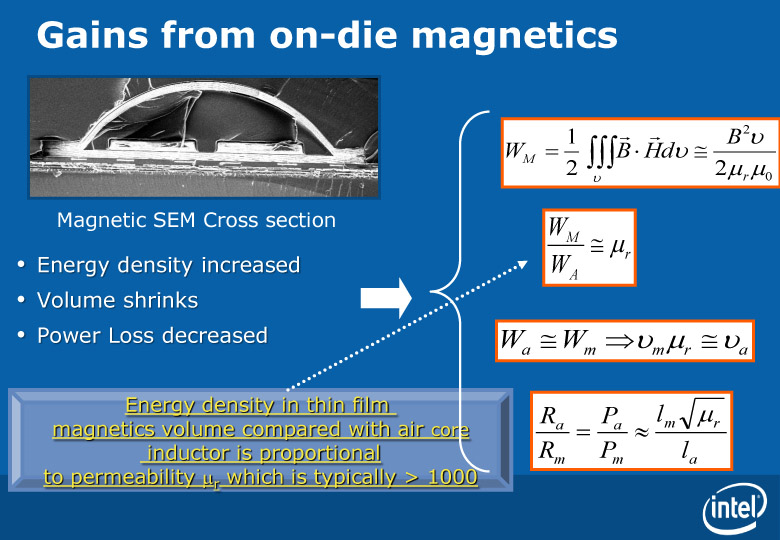

Haswell의 패키지 트레이스 인덕터는 Intel의 FIVR 개발의 로드맵에서는 아직도 중간 지점에 불과하다. 논문 발표 수준에서 이미 Intel은 한층 더 그 앞에 온다이 통합 인덕터의 기술도 2010년에 발표했으며, 프로토 타입 인덕터 및 프로토 타입 칩의 데이터도 공개하고 있다. 미래 온다이에 인덕터를 통합한 CPU도 등장하는 것은 거의 틀림 없다.

완전히 인덕터도 통합한 FIVR의 장점 중 하나는 보다 패키지 크기가 작은 칩에 FIVR 기술을 탑재 할 수 있는 것이라고 보여진다. Haswell에 채용한 패키지 트레이스 인덕터는 서브스트레이트 내에서 일정 면적을 필요로 한다. 그러나 인덕터를 온다이에 통합한다면, 이러한 제약은 없다. 모바일 용의 다이가 작고 핀 수가 많은 칩도 VR을 완벽하게 통합하기 쉬워진다. 물론 완전한 통합에 의해 보다 빠른 스위칭 속도도 장점이다.

FIVR 기술은 현재 PC 용 Haswell에서는 노트북 PC에서 뛰어난 성과를 발휘하고 있다. 그러나, Intel은 FIVR 연구의 초기 단계부터 서버 CPU 에서의 사용을 강조해 왔다. 학회 발표를 봐도 powerSOC (International Workshop on Power Supply on Chip)에서 서버 CPU 용의 FIVR의 방향성을 보여주고, ISSCC에서 매니 코어 테스트 칩에 VR을 통합하고, APEC에서 온다이 인덕터를 통합한 VR 칩을 발표했을 때도 서버 CPU에 공급할 수 있는 것을 강조하는 등 오히려 서버와 매니 코어의 연구에 초점을 맞추고 있는 것으로 보였다.

실제로 현재는 서버 및 슈퍼 컴퓨터야말로 전력 효율이 문제가 되고있다. 그리고 서버 및 HPC 솔루션은 CPU 코어 수가 많기 때문에 FIVR 의한 세밀한 전압 제어 효과가 오르기 쉽다. 실제로 IBM은 최대 CPU 칩인 Power8에 VR을 통합해 왔다. 따라서 Intel도 사용할 수 있다고 확인된 단계에서 서버 CPU에 FIVR 기술을 가져오는 것으로 보인다. 또한 그만큼의 전류량을 지원하는 FIVR 테스트 칩도 발표하고 있다.

[분석정보] Intel이 ISSCC에서 15 코어 Ivytown과 Haswell의 FIVR 기술 등을 발표

[분석정보] Intel의 "Ozette"칩에서 Haswell(하스웰)까지의 전압 레귤레이터 통합의 길

[분석정보] Intel이 Haswell 디자인 정보를 Hot Chips에서 발표

[분석정보] 인텔(intel) CPU의 큰 이정표가 될 하스웰(Haswell) 드디어 등장

[아키텍처] IDF 2013 Beijing에서 공개된 하스웰(Haswell)의 절전 & 오버 클러킹 기능

[정보분석] 배터리로 20일간 아이들 상태로 가능한 차세대 하스웰 Ultrabook

[정보분석] Hasell(하스웰) 최강의 무기 통합 전압 조절기

[아키텍처] IDF 2012 인텔 차세대 주력 CPU Haswell(하스웰) 공개

[정보분석] IDF 2011 인텔 하스웰(Haswell)의 다이와 절전 기술

[아키텍처] 환경 조건을 이용하여 성능을 끌어 올리는 터보 모드(전압 레귤레이터 전압 조절기)

[정보분석] IDF 2005 저스틴 래트너 미래의 기술

'벤치리뷰·뉴스·정보 > 아키텍처·정보분석' 카테고리의 다른 글

| [분석정보] 총 출전하는 스마트폰용 64bit SoC (0) | 2014.03.10 |

|---|---|

| [분석정보] 하스웰의 고성능 그래픽의 열쇠 Intel 제조 eDRAM의 상세 (0) | 2014.03.10 |

| [분석정보] Intel, MWC에서 각종 휴대폰 용 무선 기술을 시현 (0) | 2014.02.27 |

| [분석정보] ASUS, MWC에서 IA 버전 Android 탑재 제품만을 전시 (0) | 2014.02.27 |

| [분석정보] Intel, Merrifiled / Moorefield 탑재 64bit Android 스마트폰을 시현 (0) | 2014.02.25 |

| [MWC 2014] HP 최초의 Bay Trail + 64 bit Windows의 10 인치 WUXGA 태블릿 (0) | 2014.02.25 |

| [분석정보] Intel, 22nm의 스마트폰 Atom Z3400, 3500 발표 (0) | 2014.02.24 |

| [분석정보] Intel, Ivy Bridge-EX Xeon E7 v2 패밀리.최대 15코어 CPU 메모리 용량은 최대 1.5TB (0) | 2014.02.20 |