Transmeta 부회장 겸 CTO인 데이비드 디첼 씨

장소 : 미국 캘리포니아 산호세 페어몬트 호텔

기간 : 10월 13일 ~ 16일 (현지 시간)

마이크로 프로세서 관련 컨퍼런스인 Microprocessor Forum 2003, 미국 캘리포니아 산호세에 있는 페어몬트 호텔에서 현지 시간으로 13일부터 4일간에 걸쳐 개최된다.

어제는 세미나만 있었고 실제 회의는 오늘 내일 이틀간 개최된다. 컨퍼런스 첫날인 오늘은 Transmeta가 Crusoe의 후계가 되는 Efficeon (에피시온)의 세부 사항을 공개했으며, VIA Technologies가 Eden-N 이라는 저전력 CPU를 발표하는 등 저전력 CPU가 주목 받았다.

본 보고서에서는 오전중에 행한 발표 속에서 Transmeta 부회장 겸 CTO의 데이비드 디첼 씨에 의한 강연에서 밝혀진, Efficeon에 대한 자세한 내용을 전한다.

1MB의 L2 캐시, 11 개의 연산 유닛을 구비한 Efficeon

Efficeon의 블록 다이어그램. 노스 브릿지의 기능은 CPU에 통합되어

메모리 컨트롤러, AGP 컨트롤러, HyperTrasport 인터페이스 등을 내장하고 있다

디첼 씨가 발표한 Efficeon 마이크로 아키텍처의 자세한 내용은 다음과 같은 것이다.

11 개의 연산 유닛 (로드 / 스토어 / 32bit 가산기 × 2, 정수 연산 ALU × 2, 엘리아스 × 1, 제어 × 1, 부동 소수점 연산 / MMX / SSE / SSE2 연산 × 1, MMX / SSE / SSE2 연산 × 1, 분기 × 1, 실행 × 2)

64의 32bit 정수 연산 레지스터, 64의 80bit 부동 소수점 연산 레지스터, 4 개의 프레디 케이트 레지스터, 128KB의 L1 명령어 캐시 (4웨이 세트 어소시에이티브, 64byte 라인) + 64KB의 L1 데이터 캐시 (8 웨이 세트 어소시에이티브, 32byte 라인)

1MB의 L2 캐시 (ECC 기능과 4웨이 세트 어소시에이티브)

기본적으로는 종래대로의 VLIW (Very Long Instruction Word) 프로세서이지만, 기존의 Crusoe가 4개의 32bit 명령을 정리해서 128bit 단위로 실행하고 있던 것에 비해, Efficeon에서는 32bit 명령을 8개를 정리해 256bit 단위로 실행한다. 이에 따라 최대 8명령을 1클럭 사이클로 실행할 수 있게 된다.

Crusoe와 Efficeon의 차이. Crusoe는 32bit의 명령을 4개의 병렬 실행 128bit의

아키텍처를 채용하고 있었지만, Efficeon에서는 32bit의 명령을 8개의 병렬 실행

256bit의 아키텍처를 채용하고 있다

Efficeon에서는 11의 실행 유닛을 내장하고 있어, 이것으로 8개의 명령을 병렬로 실행

Efficeon의 CMS는 기존의 Crusoe 용 CMS에 비해 크게 개선

Efficeon의 평면도. 다이 크기는 0.13μm (130nm) 공정으로 119 제곱 mm,

90nm 공정에서 68 제곱 mm가 된다.

Efficeon 에서는 기존의 코드 모핑 소프트웨어 (CMS)보다 새로운 CMS 5.0 이 채용되어 있다. x86 명령을 atom 이라 부르는 마이크로 명령으로 변환하고, CMS에 의해 명령 실행 순서가 최적화 되어 파이프 라인에 밀어넣는 구조로 되어 있다. 정수 연산 파이프 라인은 6 단계로 부동 소수점 연산에서는 8 단계로 처리된다. CMS 5.0 에서는 256bit VLIW 명령의 최적화, 로드 / 스토어의 기능을 최적화 한 어드레스 엘리아스 체크 기능 등 기존의 CMS 4.X 보다 더 최적화가 진행되어 있다고 한다.

Efficeon도 Crusoe처럼 노스 브릿지 해당하는 기능도 통합되어 있다. 메인 메모리는 DDR400 까지 지원 가능하지만, JEDEC에서 DDR400의 SO-DIMM의 사양을 책정하고 있지 않기 때문에, 실제로는 DDR333까지가 실용이라는 것이다.

AGP 컨트롤러도 내장되어 있어 최대 AGP 4X 모드로 동작한다. 여기에, 사우스 브릿지와의 연결은 Athlon 64 패밀리와 같은 HyperTransport 가 채용되어 있으며, 상하 데이터 버스폭은 8bit 폭씩, 800MT / sec (즉 800MHz 해당)에서 1.6GB / sec의 대역폭을 실현한다. 사우스 브릿지는 NVIDIA의 nForce3 Go120, ULi (ALi)의 M1563M의 하나가 이용된다.

Efficeon 마이크로 아키텍처의 설명.

정수 연산 파이프 라인은 6 스테이지, 부동 소수점 연산은 8 스테이지다

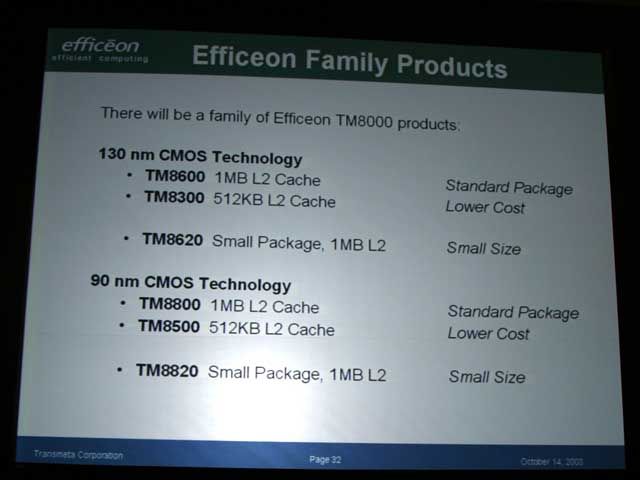

0.13μm 세대에서는 TM8600, TM8300, TM8620의 3개의 모델이 준비된다

첫 번째 세대의 Efficeon 다음의 3 제품이 준비되어 있다.

TM8600 : 1MB L2 캐시 + 일반 패키지 (29 × 29mm)

TM8300 : 512KB L2 캐시 + 일반 패키지 (29 × 29mm)

TM8620 : 1MB L2 캐시 + 소형 패키지 (21 × 21mm)

또한 동작 주파수 및 열 설계 소비 전력은 다음과 같다.

1.3GHz / 14W

1.2GHz / 12W

1.1GHz / 7W

1.0GHz / 5W

이들 제품은 모두 TSMC의 0.13μm 공정 방식으로 제조되는 것이며, 4분기에는 출하가 개시 될 예정이다. 주목할 점은 동작 주파수와 열 설계 전력의 관계다. 기존의 Crusoe는 어느 제품이라도 7W 라는 열 설계 전력을 밑돌았지만, Efficeon는 1.2GHz와 1.3GHz는 12W, 14W로 기존보다 높은 열 설계 전력이다.

CPU의 열 설계 전력이 7W 이하면 10.4인치 급 액정을 탑재한 미니 노트북뿐만 아니라 12인치 급의 액정을 탑재한 서브 노트북 클래스도 대상으로 한다.

더욱, 2004년에는 90nm 공정판의 Efficeon이 예정되어있다. 이 90nm 공정판의 Efficeon에서는 제조하는 공장이 TSMC에서 후지쯔의 "아키루 기술 센터"로 변경된다. 90nm 공정을 이용한 Efficeon는 다음과 같은 제품 이름이 된다.

TM8800 : 1MB L2 캐시 + 표준 패키지

TM8500 : 512KB L2 캐시 + 표준 패키지

TM8820 : 1MB L2 캐시 + 소형 패키지

이 90nm 버전 공정은 다음과 같은 동작 주파수, 열 설계 전력의 제품이 준비된다.

2.0GHz / 25W

1.8GHz / 12W

1.6GHz / 7W

1.4GHz / 5W

1.0GHz / 3W

또한 디첼 씨는 "3세대 제품으로 더욱 새로운 기능을 추가한 제품을 90nm 내지 65nm 공정으로 2005년에 발표하겠다"고 말해 향후도 Efficeon 라인을 확장해 나간다는 로드맵을 공개했다.

Efficeon의 로드맵.

2004년에는 90nm 공정판을 2005년에는 기능을 확장한 버전을 투입한다고 밝혔으며

Efficeon의 제품 라인업.

패키지, L2 캐시 용량의 차이 등으로 각 세대마다 3제품이 준비된다

Pentium M 900MHz와 호각의 성능을 발휘하는 TM8600 1.1GHz

Efficeon의 벤치 마크 결과. 초 저전압 판 Pentium M 900MHz와

TM8600 1.1GHz를 비교해 거의 호각이라는 결과가 됐다.

디체루 씨는 강연에서 TM8600 1.1GHz의 벤치 마크 데이터를 밝혔다.

같은 7W의 열 설계 소비 전력에 있는 초 저전압 판 Pentium M / 900MHz와 비교하여 CPUmark99, MobileMark2002, SYSmark2002, PCMark2002 CPU, Business Winstone 2001 등의 실제 응용 프로그램 벤치 마크 데이터도 공개되어 CPUmark99와 SYSmark2002에서 TM8600가 상회, 그 외에는 초 저전압 판 Pentium M / 900MHz가 상회하는 결과가 공개됐다.

여기에 실 애플리케이션의 벤치 마크 이외에도 FPU의 성능을 보여주는 LINPACK 100x100에서 TM8600 1.1GHz가 초 저전압 판 Pentium M 900MHz의 1.3 배의 점수를 보인 데이터가 공개되었다.

특히 주목되는 것은, 아이들 때의 소비 전력에 관한 데이터이다. 아이들 때의 소비 전력이 낮으면 배터리 수명에 큰 영향을 미치는 평균 소비 전력이 떨어지기 때문에 낮을수록 배터리 수명을 늘릴 수 있게된다.

디첼 씨는 CPU + FSB + 노스 브릿지 + 메모리에서 초 저전압 판 Pentium M 900MHz와 TM8600 1.1GHz를 비교한 데이터를 제시 "Efficeon는 Pentium M에 비해 아이들시의 소비 전력은 무려 1/8" 이다 라고 말하며 그 상세한 데이터를 공개했다. 이에 의하면, Pentium M 900MHz에서 1.45W의 아이들 때의 소비 전력이 Efficeon 에서는 불과 0.18W에 불과하다 말한다.

전 모델 Crusoe 에서도 그랬지만,이 점은 Pentium M에 대한 Efficeon의 이점 1가지라 말할 수 있다. 즉, 열 설계 전력이 같아서, 케이스의 크기와 배터리가 같으면, Efficeon을 탑재한 노트 PC 쪽이 장시간 배터리 구동이 할수 있는 가능성이 높다.

부동 소수점 처리 능력을 보이는 LINPACK 100x100에서

초 저전압 판 Pentium M 900MHz의 1.3 배의 결과

아이들시의 소비 전력을 나타내는 그래프.

TM8600 1.1GHz는 초 저전압 판 Pentium M / 900MHz 불과 1/8 이라고

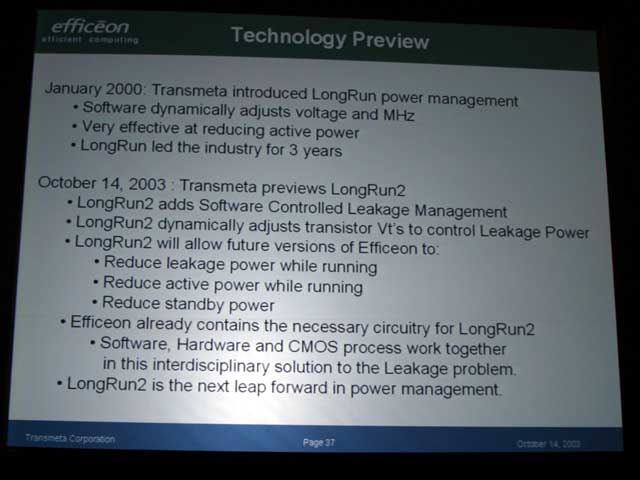

누설 전류를 소프트웨어로 제어하는 LongRun2 프리뷰

최첨단 공정방식의 약점인 누설 전류를 소프트웨어적으로 해결하는 LongRun2

또한 디체루 씨는 회사가 Crusoe에서 채용해 온, CPU의 소비 전력을 억제하는 기술인 LongRun 기술의 후속 기술로 LongRun2를 계획하고 있는 것도 밝혔다.

LongRun이 Intel의 SpeedStep 기술과 마찬가지로 CPU의 구동 전압 / 동작 주파수를 동적으로 변화시킴으로써 에너지를 절전을 실현하고 있는것에 비해 LongRun2에서는 노리고 있는 부분이 크게 다르다.

왜냐하면 LongRun2는 제조 공정 방식의 미세화에 의해 심각해지고 있는 누설 전류 (리케이지)를 컨트롤 하는 기술이기 때문이다.

"누설 전류의 문제는 이제는 업계 공통의 걱정이다. 그 문제를 해결하기 위한 기술이 LongRun2 이다"(디첼 씨)을 통해 이 LongRun2을 이용해 누설 전류를 1/70 할 수 있다고 한다. 실제로, LongRun2 의해 누설 전류를 줄이는데 성공했다는 비디오도 공개하고 LongRun2가 유효화 되기 전에는 144mW 였던 LongRun 유효화 후에는 2mW로 줄어들고 있어 확실히 큰 효과가 있는 것 같다.

다만 디첼 씨는 이 LongRun2에 관해서 자세한 얘기는 없었다. 밝혀진 것은 LongRun2는 하드웨어 기능과 소프트웨어 기능의 조합으로 트랜지스터의 Vt를 동적으로 조정해 누설 전력을 절감하는 구조 뿐이다.

또한 이번 발표된 1세대 Efficeon 에는 이 LongRun2 기능은 탑재되어 있지 않다. 디첼 씨는 "미래의 Efficeon에는 LongRun2 기능을 탑재한다"고 설명하고, 디첼 씨가 밝힌 로드맵에서 설명된 90nm 공정판 내지는 65nm 공정판 등에서 채용될 것이다.

현재 반도체 업계에 누설 전류 문제는 "고질병"이 되었다.

LongRun2의 비디오 데모.

실제로 LongRun을 사용해 144mW가 2mW까지 내려가는 모습이 데모

LongRun2는 미래의 Efficeon 제품에 탑재 될 예정

2003년 10월 15일 기사 입니다.

[아키텍처] 전력 효율성에 초점을 둔 인텔 연구개발 (PARROT)

[고전 2001.07.31] 이번 전쟁은 I/O 버스 전쟁이다 드이어 격돌 Hyper Transport 대 3GIO

[분석정보] Many-Core CPU로 향하는 Intel. CTO Gelsinger 인터뷰 1/2부

[분석정보] CPU와 메모리의 속도 차이를 해소하는 캐시의 기초지식

'벤치리뷰·뉴스·정보 > 고전 스페셜 정보' 카테고리의 다른 글

| [고전 2004.03.05] 멀티 코어 + 멀티 스레드 + 동적 스케줄링으로 향하는 IA-64 (0) | 2005.12.03 |

|---|---|

| [고전 2003.11.21] 939핀 플랫폼과 90nm 공정 도입을 서두르는 AMD (0) | 2005.11.11 |

| [고전 2003.11.07] AMD, CPU 로드맵을 업데이트 (0) | 2005.11.11 |

| [고전 2003.10.18] 모든 CPU는 멀티 스레드로, 명확하게 된 CPU의 방향 (0) | 2005.11.10 |

| [고전 2003.09.16] K9는 DDR2 메모리와 차세대 HyperTransport에 대응 (0) | 2005.11.09 |

| [고전 2003.09.24] AMD 64bit 프로세서 Athlon 64 정식 발표 (0) | 2005.11.09 |

| [고전 2003.09.19] EFI 프레임 워크의 도입으로 변하는 BIOS (0) | 2005.11.09 |

| [고전 2003.09.12] AMD의 차기 CPU 코어 "K9"는 2005 년에 등장인가? (0) | 2005.11.09 |