2010년 이후 무어의 법칙 유지가능

트라이 게이트 트랜지스터

인텔 주식회사는(인텔 재팬) 19일 언론을 대상으로 설명회를 개최하고 새로운 3차원 구조의 트랜지스터 "트라이 게이트 트랜지스터 '를 발표했다.

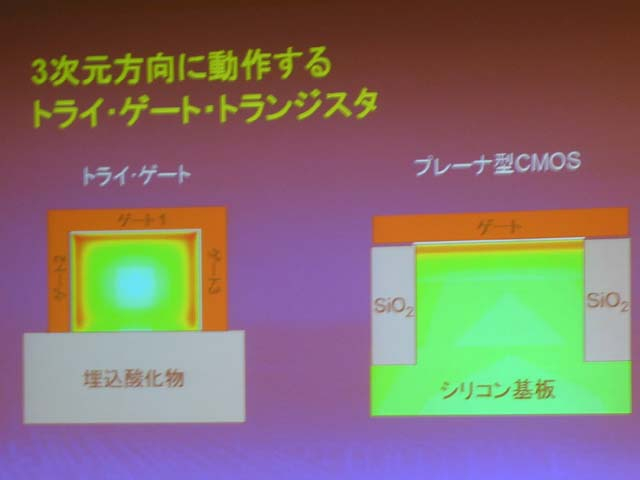

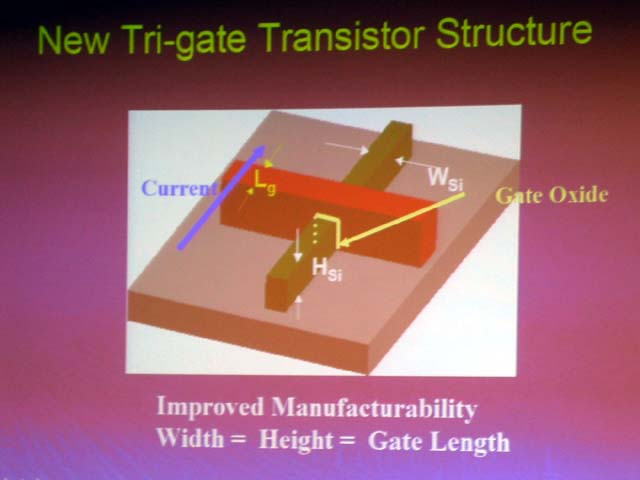

"트라이 게이트 트랜지스터 '는 정육면체 구조의 트랜지스터로 기존의 평면(2 차원) 트랜지스터의 표면에 해당하는 상단의 수평면과 양쪽에 수직 벽면을 갖춰 이에 따라 전기 신호를 통할 수 있다. 전기신호 통과 영역이 3배로 확대되는 것으로, 나노 영역에서의 동작효율을 향상시킬뿐 아니라, 같은 게이트 크기의 평면 (2 차원) 형에 비해 20% 많은 전류를 흐르게 수 있다.

설명회에서는 인텔 주식회사 이사 개발 · 제조 기술 본부장 성 코지 씨가 미국 오리건 Intel의 나노 기술 연구 시설에 대해 설명. 그러면 Intel 기술 · 제조 본부 로직 기술 개발 부문 컴포넌트 리서치 디렉터 제럴드 마싯쿠 씨가 이 기술에 대해 설명했다.

마싯쿠 씨는 먼저 "트라이 게이트 트랜지스터 '를 2010 년 이후에 걸쳐 무어의 법칙을 유지할 수있다" 트랜지스터 연구의 돌파구 "라고 평가했다.

평면형 트랜지스터의 미세화를 촉진

평면형 타입, 무어의 법칙은 2009년까지 유지. 트라이 게이트 트랜지스터는 이 로드맵 이후에 무어의 법칙을 유지해 나갈 것으로 예상되는 기술.

평면형 트랜지스터의 과제는 누설 전류

Intel은 평면형 트랜지스터의 미세화를 추진하고 있으며, 로드맵대로 가면 2009년에는 게이트 길이 15nm, 32nm 노드까지 미세화가 가능하게 된다고 한다. 그러나 planar 형 그대로 미세화를 계속하면 누설 전류가 높아져 불필요한 전력 소비와 구동 전압의 향상 등의 폐해가 일어난다. 인텔이 2001년 11월에 발표 한 "테라 헤르츠 트랜지스터"는 고유 전율 게이트 절연막 (High-k)과 렌즈 소스 드레인 구조의 채용으로 따로 누설 전류를 감소하는 방법 이었지만, 미세화를 진행 시키면 나노급 미세 실리콘 층의 두께 제어가 필요한 등 제조상의 문제도 있었다

"트라이 게이트 트랜지스터 '는 테라헤르츠 트랜지스터의 아키텍처 확장에 자리 매김하고 있으며, 전체 고갈형 실리콘 층 위에 상단의 수평면과 양쪽에 수직 벽면을 갖춘 전기 신호가 통과 영역을 3 배로 확대.

이번에 개발한 것은, 게이트 길이 60nm 트라이 게이트 완전 고갈형 CMOS로 소비 전력을 크게 낮추면서 트랜지스터의 온 / 오프 속도 향상을 행할 수 있으며, 일반적인 노광 기술을 사용해 SOI 두께 제어가 충분히 가능해지는 등, 제조면에서의 문제도 해결할 수 있다.

트라이 게이트 트랜지스터(왼쪽)

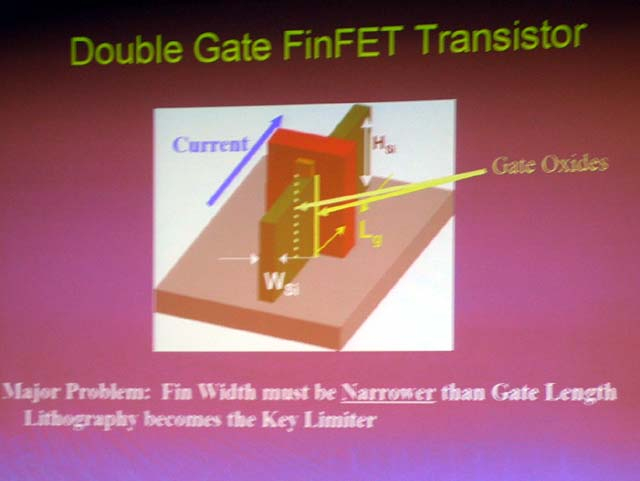

마싯쿠 씨는 "반도체 업계의 동향도 이러한 비 planar 형으로 전환하고 있다"고 상황을 설명한 후 업체가 발표하는 더블 게이트 구조 등에 대해서도 언급하고 "더블 게이트 FinFET는 Fin의 폭이 게이트 길이보다 짧게 해야하기 때문에, 제조상의 어려움이 따른다. 트라이 게이트는 게이트 길이와 핀의 폭 / 높이가 공통 때문에 제조가 용이하게 된다 "등 트라이 게이트 구조의 장점을 설명했다.

트라이 게이트

더블 게이트 FinFET

2002년 9월 19일 기사 입니다. 블로그 날짜 설정이 2003년까지 밖에 안되기 때문에...;;;;

먼 훗날인 10년뒤 2012년 22나노 아이비브릿지 제조에 사용된 트라이게이트

이것도 보여준게 2002년이면 이걸 연구는 수년 전부터 했다는 얘기인데..

[01년11월27일] 인텔 테라 헤르쯔 트랜지스터 기술 발표

'벤치리뷰·뉴스·정보 > 고전 스페셜 정보' 카테고리의 다른 글

| [고전 2003/02/17] 100MHz 부터 3066MHz까지 65 CPU 벤치마크 (0) | 2005.11.02 |

|---|---|

| [고전 2002.11.14]Pentium 4 3.06GHz 빠른 리뷰 Hyper-Threading의 효과는 얼마나? (0) | 2005.10.11 |

| [고전 2002.10.04] Pentium 8 후보 Nehalem 아키텍처 (0) | 2005.10.10 |

| [고전 2002.09.27] 밝혀진 차세대 직렬 버스 "PCI Express" 사양 (0) | 2005.10.09 |

| [고전 2002.09.12] 7700만 트랜지스터를 전력효율 향상에 쓴 Banias (0) | 2005.10.09 |

| [고전 2002.09.12] Hyper-Threading Technology를 지원하는 HTT Pentium 4 3.06GHz (0) | 2005.10.09 |

| [고전 2002.09.11] 이것이 Banias 플랫폼이다 CPU 마이크로 아키텍처 편 (0) | 2005.10.09 |

| [고전 2002.09.10] Intel Developer Forum Conference Fall 2002 기조 강연 리포트 (0) | 2005.10.09 |