23 일부터 미국 샌프란시스코에서 개최중인 Intel Developer Forum (IDF)에서 화제의 중심은 Intel이 "차세대 마이크로 아키텍처"라고 부르는 차세대 프로세서 "Merom (메롬, 개발 코드 네임)" 및 "Conroe (콘로 개발 코드 명)" 등 2006년 하반기에 출시될 CPU이지만, 2006년 1분기에 출시를 예정하고 있는 Napa 플랫폼의 첫 번째 CPU로 등장하는 "Yonah (요나 개발 코드명)" 라는 듀얼 코어 CPU에 대한 정보도 일부 업데이트 되어 있다.

본 보고서에서는 IDF에서 열린 설명회 등에서 제시된 Yonah의 최신 정보를 전달하고 싶다.

공유 캐시로 더 최적화 된 듀얼 코어를 실현하는 Yonah

사용자에 대한 Yonah의 매력은 모바일 PC 용으로 최초의 듀얼 코어 CPU라는 점일 것이다.

듀얼 코어로 Yonah의 가장 큰 특징은 공유된 L2 캐시에서 엿볼 수 있다. 지금까지 등장한 듀얼 코어, 예를 들면 Intel 자신의 Pentium D와 AMD의 Athlon 64 X2 등은 모두 각각의 코어에 L2 캐시를 탑재하고 있었다. 이에 비교해 Yonah는 2 개의 코어가 캐시를 공유하는 구조를 채용하고 있다.

독특한 것은, 각 코어에 할당 L2 캐시의 용량은 동적으로 변경할 수 있다. 예를 들어, 두 개의 코어 중 1번째 코어가 1.5MB를 사용하고 두 번째 코어는 0.5MB 만 이용한다는 할당이다. 이 할당은 동적으로 변경 가능하므로 CPU의 요구에 따라 순차적으로 변해 간다.

각각 L2 캐시가 포함된 Pentium D의 경우에는 한쪽의 코어의 캐시가 별로 사용되지 않아도 그것을 다른쪽에 할당 할 수 없기 때문에 효율성 측면에서 공유 캐시에 다소 떨어진다.

Yonah의 내용을 설명하는 슬라이드

Yonah의 기본적인 아키텍처. 가장 큰 특징은 공유형 L2 캐시를 갖추고 있을 것

Yonah는 L2 캐시 할당을 동적으로 변경할 수 있다.

이렇게 하면 캐시 용량을 효율적으로 사용할 수 있다

마이크로 명령 실행시 효율 개선에 의해 미디어 처리시의 능력을 개선

Yonah의 또 다른 특징은 Intel의 "Digital Media Boost"라고 부르는 미디어 처리 능력의 개선이다. Intel 모바일 마이크로 프로세서 그룹 CPU 검증 매니저 로니 코너 씨는 "Yonah는 내부 구조의 재검토에 의해, SSE 명령어 실행 효율을 개선하고 있다"라고 말하고, 그 구체적인 예로서 몇 가지 개선점을 보였다.

Yonah는 SSE 명령어 디코더의 처리량을 개선하고 있다. 예를 들어, 지금까지 SSE 명령어를 이용한 가산을 행하는 경우, 4개의 마이크로 명령으로 분할하여 실행되고 있던 것이 하나의 마이크로 명령으로 수행 할 수 있게 되었다고 한다. 이 밖에 SSE2에서 셔플과 언팩 같은 명령을 실행할 경우, 불필요한 연산을 없애는 등에 의해 연산에 걸리는 지연 시간을 줄이고 있다. 이는 경우에 따라 30% 가까운 효율을 향상시킬 수 있다고 한다.

또한 새로 Prescott에서 지원되는 SSE3에도 대응하고 있으며 부동 소수점 연산시 데이터 프리 페치를 하는 등으로 성능을 개선하고 있다고 한다.

Banias / Dothan에서는 이러한 미디어 처리 성능은 약점으로 얘기되어 왔지만, 이러한 개량에 의해, Yonah는 이전 보다는 미디어 처리 성능이 개선된다.

Yonah는 미디어 성능 개선이 하나의 테마

Yonah는 마이크로 명령어를 개선하여 불필요한 명령을 줄이고

SSE 명령 실행시 성능을 향상

SSE2 셔플 및 압축 풀기 명령 실행시의 효율도 개선

부동 소수점 연산의 성능도 데이터 프리 페치 및 버퍼의 추가 등으로 개선하고 있다

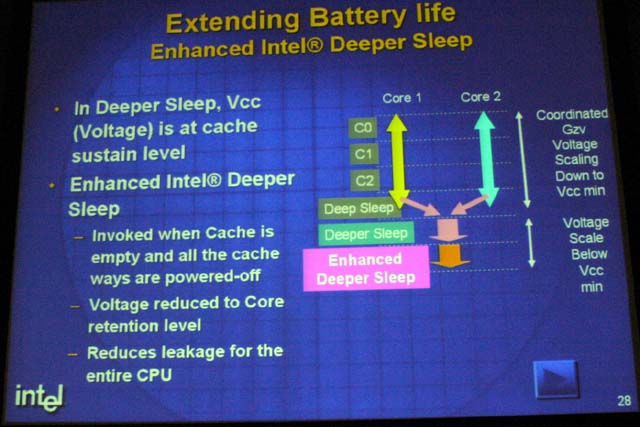

C4보다 더 전원 관리를 실현하는 "Enhanced Deeper Sleep"

Yonah는 "Intel Dynamic Power Coordination"라는 절전 기술이 탑재되어 있다. 이것은 CPU의 상태를 각 코어마다 변화시키는 구조로, 예를 들어, 2개중 1개의 코어가 절전 상태로 또 하나의 코어만 작동하는 사용법이 가능하게된다.

OS에 따라 CPU 사용률이 낮고, 단일 스레드 처리 밖에 수행하지 않은 경우에는 2개 CPU 코어 중 하나는 놀고있는 상태가 되므로 그것을 슬립 모드로 전환해 CPU의 소비 전력을 조금이라도 낮추려는 시도다.

ACPI는 CPU의 전원 상태를 C0 ~ C3의 4 단계로 규정하고 있다. 각각 어떤 상태 일까 말하면 다음과 같이 되어 있다

· C0 정상 작동 상태 : OS 등 응용 프로그램이 실행

· C1 Halt 상태 : Halt 명령을 실행하여 CPU 코어의 클럭이 중지

· C2 클럭 중지 : CPU 코어 및 버스 클럭이 중지

· C3 Deep Sleep : 클럭 생성기도 중지

· C4 Deeper Sleep : Vcc (CPU의 공급 전압)을 감소

CPU는 C0> C1> C2> C3와 서서히 상태를 변경해 가는 것으로, CPU 내부 클럭을 중지하고 , 점차 CPU의 작동을 멈추어 가는 일을 하고 있다.

또한 Intel에서는 독자적으로 C4라는 모드를 설정하고 있다. Intel이 DeeperSleep 라고 부르는 모드로 130nm에서 제조된 모바일 Pentium III 기준으로 이 모드가 추가되었다. C4는 CPU에 공급되는 전압 (Vcc 파라미터에서 설정되는)을 저하시켜, CPU의 소비 전력을 더욱 감소시킨다.

Yonah는 각각의 CPU 코어가 작동 상황에 따라 C0에서 C3 사이를 왕래한다. 예를 들어, 첫 번째 코어가 C0 (동작 상태)에 있을 때, 사용되지 않은 두 번째 코어는 C3로 전환하는 등의 움직임을 한다. 그러나 Yonah는 공급되는 전압은 1 계통 밖에 없기 때문에 C4로 전환하는 경우에는 2개의 코어가 갖추어져 C4로 이행할 필요가 있다.

Intel은 Yonah에서 "Enhanced Deeper Sleep"또는 DC4라고 부르는 더욱 확장된 C4 상태를 추가하고 있다. 이 DC4는 L2 캐시에 공급되는 전압도 낮추고, CPU의 소비 전력을 낮춘다. 그러나 공급 전압을 낮추는 것은 L2 캐쉬의 전원을 끊는 것과 같은 것이므로, L2 캐시의 내부에 축적된 데이터를 메인 메모리에 대피시킬 필요가 있다. 따라서 Yonah는 DC4로 이행하기 전에 캐시의 내용을 메모리에 보낸 다음 DC4 상태로 이행하게 된다.

Yonah는 기존의 C0에서 C4 이외에 DC4라는 확장된 DeeperSleep 모드가 추가

Enhanced Deeper Sleep에서는 L2 캐시의 내용을 메모리에 대피시킨 후

L2 캐시의 전압을 떨어 뜨려 새로운 에너지를 절감하는

평균 소비 전력은 Dothan과 비슷한 수준까지 내린 Intel

Yonah 디자인을 시작했을 때에는 Dothan의 5배의 평균 소비 전력이 되고 있었지만,

다양한 절전 기술을 구현함으로써 궁극적으로 Dothan과 비슷한 범위까지 낮추는 것이 가능하게 되었다

신경이 쓰이는 것은 이러한 개혁이 Yonah의 평균 소비 전력의 감소에 기여하는지 여부이다. 평균 소비 전력의 증대와 배터리 구동 시간은 반비례의 관계에 있어, 평균 소비 전력이 증가하면 그만큼 배터리 구동 시간은 줄어들게된다.

코너 씨는 "이 새로운 절전 기능 등으로 Yonah의 평균 소비 전력은 싱글 코어인 Dothan 코어의 Pentium M과 동일한 범위까지 낮출 수있게 됐다"라고 Yonah의 평균 소비 전력이 Dothan 과 동일한 범위까지 낮추는데 성공하고 있다고 설명했다.

이미 이전 기사에서도 지적했듯이, Intel은 OEM 벤더에 대해 Yonah의 평균 소비 전력은 Dothan와 동일한 범위 또는 약간 증가하는 정도에 머무르고 있다고 설명하고, 코어 수에 비례해, 평균 소비 전력이 크게 증가하는 것은 아니라고 한다.

OEM 메이커 관계자의 정보에 의하면, Napa 플랫폼은 칩셋의 평균 소비 전력이 Sonoma 플랫폼에 비해 저하되고 있다고 한다. 따라서 Carmel (1 세대 CMT)에서 Sonoma (현재 CMT)으로 이행 할 때 보였던 배터리 구동 시간의 감소는 너무 걱정하지 않아도 좋을 것 같다.

2006년 후반에는 Yonah에서 Merom로 이행해 나가는 Napa 플랫폼

이미 언급한 바와 같이, 2006년 후반에는 Yonah의 후속으로 데스크톱 PC 또는 서버 / 워크 스테이션과 공통의 마이크로 아키텍처를 채용한 Merom이 투입되어 칩셋의 "Calistoga"나 무선 LAN 모듈 "Golan" 결합 Napa 플랫폼으로 투입된다.

Merom은 Yonah는 지원하지 않는 EM64T 기반이며, 캐시 용량은 4MB로 확장된다. 또한 공식적으로 이야기 되고 있지 않지만, OEM 벤더 관계의 정보에 의하면, 몇 가지 새로운 확장 명령도 구현될 예정이며, 미디어 처리 능력이 더욱 강화된다.

Merom은 Yonah와 핀 호환이 가능하며, 노트북 PC 공급 업체는 Yonah을 Merom 으로 교체만으로 Merom 탑재 노트북 PC를 제조 할 수 있게 된다. 그러나 열 설계 전력은 Yonah가 31W 인 반면, Merom은 35W로 되어 있어 미리 노트북 PC 공급 업체는 35W의 CPU를 탑재하는 것을 전제로 섀시(케이스) 설계를 해 둘 필요가 있다.

사실, 대부분의 노트북 PC 공급 업체는 Napa 세대의 노트북 PC를 35W를 전제로 설계되어 있으며, 아마 많은 제품이 3분기 단계에서 Yonah에서 Merom 으로 바꾸어 제품을 출시해 가게 되는 것이다.

2005년 8월 25일 기사 입니다.

(콘로의(노트북판 메롬) 직계 조상이라 할수 있는 요나 기사 입니다. 테자스와 네할렘이(취소된 초대 네할렘) 취소된 상태에서, 모바일 그룹에서 개발한 이런 제품들 조차 없었다면 (Banias, Dothan) 네할렘 발표까지 인텔은 나락으로 떨어졌을지도 모릅니다. 이미 펜티엄3 정도.. 그 이후 정도부터 노트북 시장은 아주 커져있는 상태니까요. 데스크탑에서는 프레스컷과 AMD 64의 대결로 70%대의 점유율 이었지만, 반대로 노트북에서는 80% 중반이 넘는 점유율)

[고전 2000.2.25] 인텔 사내경합이 낳은 Willamette 1.4GHz

[고전 2000.08.25] 그래픽 통합 CPU 팀나(Timna)의 개요를 분명히-극적인 다이 크기 축소를 실현

[고전 2002.01.31] Intel은 IA-32의 64bit 확장 "Yamhill"을 개발하는 이유

[아키텍처] 폴락의 법칙에 찢어지고 취소된 테자스(Tejas)

[정보분석] Merom(메롬) 이후인 Nehalem(네할렘) 과 Gilo(길로)

[정보분석] 2년 주기로 아키텍처를 쇄신하는 Intel

[분석정보] Intel 4번째 x86 CPU 개발 센터 방갈로르

[정보분석] IDF 2005 저스틴 래트너 미래의 기술

[고전 2005.08.25] Intel이 차세대 마이크로 아키텍처 CPU를 공개

'벤치리뷰·뉴스·정보 > 고전 스페셜 정보' 카테고리의 다른 글

| [고전 2005.11.30] 마이크로 아키텍처의 변화를 반영하는 "Core"브랜딩 (0) | 2005.12.23 |

|---|---|

| [고전 2005.11.10] 보이는 인텔의 5~10년 후 CPU 아키텍처 (0) | 2005.12.23 |

| [고전 2005.08.29] IDF 2005 저스틴 래트너 기조 연설 미래의 기술 (0) | 2005.12.20 |

| [고전 2005.08.25] Intel이 차세대 마이크로 아키텍처 CPU를 공개 (0) | 2005.12.20 |

| [고전 2005.08.05] 새로운 공장 건설에서 보는 인텔의 Fab 변천 (0) | 2005.12.20 |

| [고전 2005.06.07] Mac에 Intel CPU 탑재를 잡스 CEO가 선언 (0) | 2005.12.18 |

| [고전 2005.06.01] AMD, Athlon 64 X2 발표회 (0) | 2005.12.18 |

| [고전 2005.5.25] 도선 오버 넷버스트 (0) | 2005.12.17 |