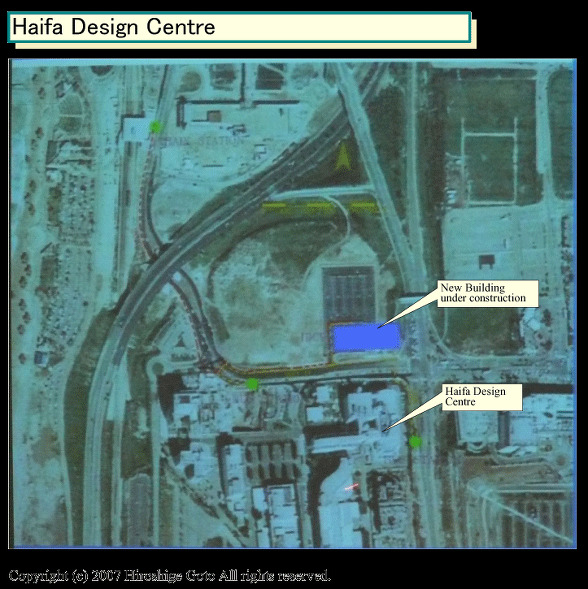

이스라엘 하이파 디자인 센터의 연구 개발

하이파 디자인 센터

Intel의 Ron Friedman (론 프리드먼) 씨

Intel은 "터보 모드"를 CPU에 구현하고 CPU 안밖의 다양한 조건의 변화에 따라 CPU 코어 단위로 성능을 강화한다. 이에 따라 시스템의 냉각능력의 범위 내에서 효율적으로 성능을 높이는 방향으로 나아가려 하고 있다. 이스라엘의 하이파 (Haifa)의 개발 시설 "Haifa Design Centre (하이파 디자인 센터)"는 터보모드의 광대한 적용을 연구하고 있다. 그리고 터보 모드 기술은 이센터에서 개발한 CPU뿐만 아니라 Intel CPU 전체에서 적용되는 것으로 보인다.

Intel은 하이파 디자인 센터에서 터보 모드의 비전에 대한 설명을 했다. 하이파 디자인 센터를 담당하는 Intel의 Ron Friedman (론 프리드먼) 씨 (Vice President, General

Manager, Mobile Microprocessors Group)는 이 센터의 CPU 개발의 기본 사상을 설명. 그 속에서 터보 모드가 광범위하게 적용되는 기술임을 강조했다.

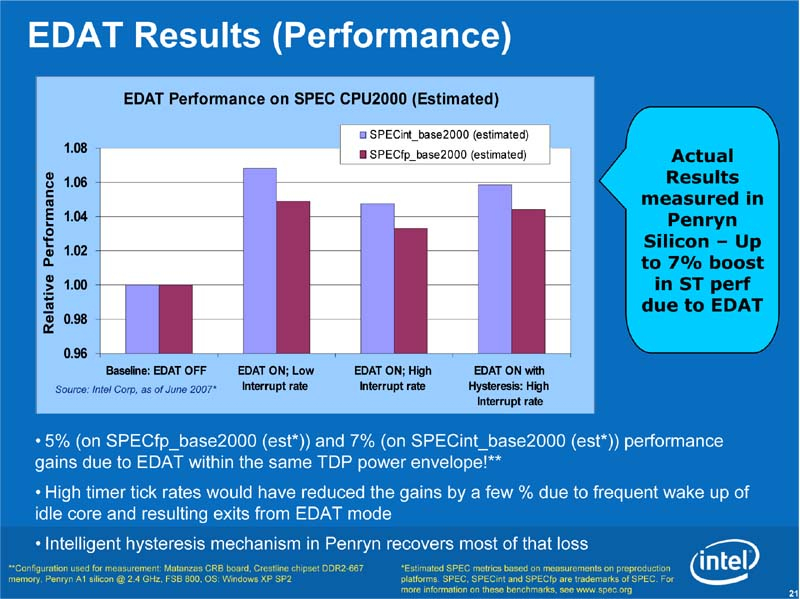

하이파 디자인 센터에서 개발한 Core Microarchitecture (Core MA)는 "Enhanced Dynamic Acceleration Technology (EDAT)"라고 부르는 터보 모드를 구현했다. EDAT는 45nm 버전의 Core 2 Duo (Penryn : 펜린)에서 활성화 된다. Intel은 Penryn의 EDAT가 단일 스레드 애플리케이션의 성능을 향상하는 기술이라고 설명했다. (펜린은 울프데일의 노트북 버전 입니다. 코어2 브랜드 제품들 자체가 원래 노트북용에서 데스크탑까지 온거라서.. 원래 메롬(콘로가 아닌, 데탑이 콘로), 펜린이 더 맞겠죠. )

"Haifa Design Centre (하이파 디자인 센터)"

구체적으로 EDAT는 듀얼코어 Penryn에서 단일 스레드 응용 프로그램을 실행할 때, 한쪽의 CPU 코어가 유휴 C3 스테이트에 들어갔을 경우, 액티브 CPU 코어의 주파수를 1 단계 올린다. 잠자는 CPU 코어로 줄어든 것의 전력 소비를 활성 상태의 CPU 코어가 소비하는 것으로 성능을 끌어 올린다.

이 EDAT 메커니즘을 통해 같은 TDP (Thermal Design Power : 열 설계 전력)의 범위 내에서, 싱글 스레드 성능을 동적으로 끌어 올릴 수있을 것으로 Intel은 설명하고 있다. Intel은 일반적으로 새로운 기능은 1 세대 이전 CPU에 숨겨진 기능으로 시험적으로 구현하여 실제 실리콘 실효성을 테스트 한다. 따라서 EDAT도 실제로는 Merom에서 구현되고 테스트 되었으며, Penryn에서 처음 활성화 될 것으로 추측된다.

"Enhanced Dynamic Acceleration Technology (EDAT)"

EDAT 구현 개요

EDAT의 성능 향상

CPU 코어 자신이 환경을 인식하고 터보에 들어가

활성화로 보여지는 EDAT 하지만 Intel의 발표를 들은 CPU 업계의 반응은 회의적인 입장도 있었다. AMD를 비롯해 여러 CPU 관계자로부터 부정적인 의견을 들었다.

의문의 하나는 하나의 코어만 높은 요구에 다른 한쪽의 코어가 C3에 들어갈 기회가 얼마나 있는가 하는 점. 또 하나는 부스트하는 것이 1 단계만으로는 성능이 그다지 업하지 않는다는 점. 따라서 EDAT 구현하고 실효성이 있는지가 의문이었던 셈이다.

하지만 이번 Core MA를 개발 한 하이파 디자인 센터 Friedman 씨는 Penryn에서 이네 이블링 되는 "터보 모드"는 미래에 EDAT에 표시된 조건뿐만 아니라 더 넓은 범위에서 적용할 생각이 있다고 밝혔다. 또한 터보 업의 수준도 1 단계에 그치지 않을 수 있다고 Friedman 씨가 밝혔다.

"재미있는 현상은 향후 프로세서 코어, 듀얼 코어, 쿼드 코어, 한층 더 그 앞으로 더욱 더 늘어가는 것이다. 그리고 (CPU의) 맥스 파워는 멀티코어 CPU의 모든 코어가 풀 대역에서 작동 때 전력(열)으로 정의되어 있다. 그러나 항상 그런 상태가 될 것은 아니다.

4 코어 중 2 코어만 풀로 작동할 때도 있고, 혹은 단 1 코어만 작동할 때도 있다. 그러면 1 ~ 2 코어가 돌어가고 다른 코어가 잠을 잘때, 좋은 성능을 얻을 수 있다고 생각된다. 또한 실내 온도가 35도 이하일 때와 플랫폼이 차가울 때, 그것을 이용하여 더 성능을 얻을 수도 있다.

우리는 이것을 터보 모드라고 부르고 있다. 먼저 CPU 자신이 코어 작동과 온도 등의 상태를 인식한다. 그리고 만약 OS가 활성 코어에 높은 성능을 요구한 때에는 활성 코어의 성능을 전력(열) 틀 속에서 최대까지 끌어 올린다. 다른 코어가 일어나거나 실온과 플랫폼의 온도 변화까지 터보 상태를 계속 "(Friedman 씨)

Penryn에서는 EDAT를 위해 중간 P 스테이트로의 오퍼레이션 포인트 단계를 변화시키지 않고, 부스트시의 주파수를 끌어 올릴 수있는 메커니즘을 구현했다. 그러나 이 구현 트리거는 CPU 코어의 유휴 상태로 제한되어 있지 않다. 즉, 같은 메커니즘으로 다른 트리거 작동 할 수있다. Penryn에 도입 된 것은 이를 위한 기본 메커니즘이며, Intel은 트리거를 점점 늘려 나갈 생각이다.

환경 조건을 이용하여 CPU의 성능을 끌어 올려

이렇게 보면, Intel이 도입하고있는 터보 모드는 포괄적인 CPU의 효율성 메커니즘임을 알 수 있다. Friedman 씨는 다음과 같이 말한다.

"터보 모드는 환경 조건을 잘 사용하면 동일한 전력 (TDP) 내에서, 보다 높은 성능을 이끌어 내기 위한 새로운 메커니즘이다. 터보 모드의 본질은 낙관주의적인 것으로서 반드시 항상 사용할 수있는 것은 아니다.하지만 사용자가 사용한 시간의 대부분에서, 터보 모드의 혜택을 얻을 수 있다고 생각하고있다.

예를 들어, CPU의 스펙은, 환경 (ambient) 온도가 35도에 정의되어있다. 그런데 사무실에서 실제로 온도가 30도 이상되는 것은 아니다. 일반 사무실은 더 낮고, 예를 들면,이 빌딩 (하이파 디자인 센터)은 23도다. 터보 모드에서는 이러한 환경 조건을 동적으로 이용한다. 환경이 바뀌면, 터보 상태에서 돌아온다. 예를 들어, (사무실을 나와) 애리조나 사막에 여행하면 환경이 바뀌고 터보 상태가 아닌 것 "

하이파 디자인 센터가 생각한 터보 모드는 일정한 열 예산 (냉각 능력의 여유)에서, CPU 코어를 효율적으로 작동시키는 메커니즘의 총칭이다. 듀얼 코어의 한쪽 CPU 코어 부스트에 머물지 않고, 모든 기회를 잡아 CPU 코어의 성능을 터보 할 것으로 보인다. 또한 터보 너비도 1 단계에 머물지 않는다. Friedman 씨는 대부분의 경우 20 % 이상의 성능 향상을 얻을 수있을 것으로 보인다.

이러한 터보 모드의 비전을 알고,이 작은 아이디어가 아니라, 향후 하이파 디자인 센터의 CPU의 기본 특징적 열쇠로 널리 활용되어 가는 것을 알 수있다. 또한, 이스라엘 개발의 CPU뿐만 아니라, Nehalem 등 Intel의 다른 디자인 센터의 CPU에 구현되어 가는 것 같다. 모바일 CPU뿐만 아니라 모든 세그먼트의 CPU에 도입 간다 추측된다.

TDP 범위 내에서 가장 높은 성능을 얻는 방법

멀티 코어 화가 진행되면 이점이 증가 터보 모드

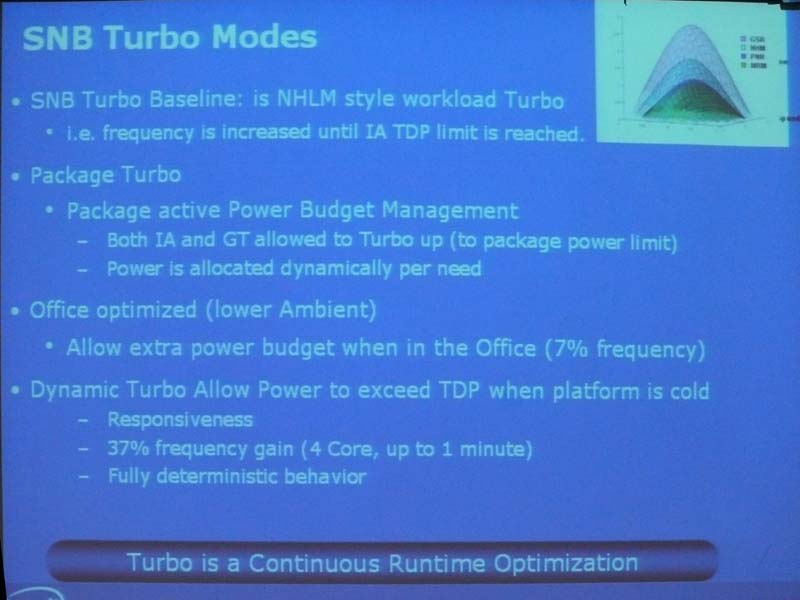

터보 모드로 전환 트리거는 다양한 조건이 상정되고 있다. (1) 멀티 코어 CPU에서 일부 CPU 코어가 유휴 상태가 된 경우를 이용하는 EDAT 형 방법 (2) 환경 온도의 변화를 이용하는 방법, (3) 플랫폼의 온도 변화를 이용하는 방법, (4)이 외에도 멀티 다이 CPU의 경우에 패키지 레벨에서 여러 다이의 전력 소비의 차이를 이용하는 방법이 있다.

(1) EDAT 형 멀티 코어의 제어는 CPU 코어 수가 많을수록 혜택이 늘어난다. 쿼드 코어 나 옥타 코어의 경우 모든 CPU 코어가 풀 가동 될 수 있는 애플리케이션은 제한된다. 그러나, CPU의 전력 효율을 높이기 위해서는, CPU 코어별로 비대화하지 않고 CPU 코어 수를 늘리는 것으로 피크 퍼포먼스를 올릴 것이 좋다. 따라서 PC와 (서버,웍스테이션,슈퍼컴퓨터가 아닌) 같이 스레드 병렬성이 얻기 힘든 소프트웨어 환경에서 스레드 수가 적은 경우와 많은 경우 모두 동적으로 런타임에 적합할 수 있는 아키텍처가 바람직하다.

터보 모드는 이러한 경우에 최적이다. 병렬형 응용 프로그램의 경우 모든 CPU 코어를 규정 주파수에서 성능을 얻는다. 그러나 스레드 병렬성이 낮은 경우에는 불필요한 CPU 코어는 절전시켜 활성 CPU 코어의 주파수를 부스트시킨다. 동적으로 어느 정도 섬세한 단위로 제어하는 것으로, 같은 TDP의 테두리 내에서 스레드 병렬성이 낮은 응용 프로그램의 성능을 비약적으로 향상시켜. 이 기술은 CPU 코어 수가 많을수록 유용하기 때문에, 쿼드 코어가 메인이 되는 Nehalem도 구현되어 있다.

Penryn의 EDAT와 미래 CPU의 예측되는 터보 모드

낮은 사무실 온도에 맞춰 터보하기

(2) 환경 온도의 변화를 이용하는 방법을 이해하려면 먼저 CPU의 냉각 능력의 산출 방법을 알 필요가 있다. 일반적으로 PC 설치 공간의 온도인 환경 온도 (Max External Ambient Temperature : Te)(본체 외부 온도 : 방온도)는 섭씨 35도로 추측된다. 본체안의 프로세서 주변 공기 온도 (Max Local Ambient Temperature : Ta)는 현재 Te를 몇번(몇도) 더한 온도로 설정된다 (PC 본체 내부는 여러 장치의 열 때 문에 PC 외부보다 온도가 더 높겠죠. 아무리 케이스 자체에 펜을 많이 달더라도요). 데스크톱의 경우 이 Ta(본체 내부온도)와 CPU의 case (CPU 히트 스프레더 온도, 쉽게 CPU 뚜껑 온도) 온도(Tc)의 차이가 열 예산이 된다. 즉, Tc의 상한이 섭씨 67도 일때 Ta가 섭씨 38도라는 스펙(기준)의 경우 두 온도의 차이인 섭씨 29도를 이용하여 CPU를 냉각할 수 있다. 이 온도 차이가 온도 예산 (temperature budget)이다. 그리고, 냉각기구의 능력은 (Tc-Ta) / TDP이기 때문에 만약 TDP가 100W 인 경우에, 29 / 100 = 0.29도 / W가 타겟의 냉각능력이 된다.

Friedman 씨가 지적하고있는 것은 여기에서 사무실 온도가 실제로는 섭씨 23도였다 경우. 섭씨 23 도의 경우는 스펙인 섭씨 35도에서 12도가 낮다. CPU를 냉각할 수 있는 온도 차이, 즉 온도 예산도 실제로는 스펙의 29 도 분이 아닌, 41도 분을 확보할 수 있게 된다. 그런데, 냉각기구 자체는 (Tc-Ta) / TDP로 설계되어 있다. 따라서 Ta이 스펙보다 저하분 만큼, 냉각 능력이 실질적으로 늘어난다. 그만큼 터보 할 수 있는 여지가 발생하게 된다. 숫자 놀이로 보이기도 하지만 , Intel은 환경 온도에 맞는 제어에 따라 몇 %의 터보가 가능하다고 보고있다. (쉽게 말하면 40도의 공기를 쎄게 보내서 열을 식히는 경우에 비해서, 20도의 공기를 동일한 쎄기로 보내서 열을 식히면 20도의 공기로 식히는게 열이 더 빠르게 식죠.)

환경 온도를 이용할 경우에는, (1)의 활성 CPU 코어 수를 기반으로 하는 제어와는 관계가 없다. 그러나 당연히 조합에 있다. (1)과 (2)의 조합으로 활성화 CPU 코어의 성능은 정격보다 훨씬 업이 가능할 것으로 추측된다. 그 결과, 20 % 등 성능 향상을 얻을 수 있을 가능성이 있다.

플랫폼의 온도를 이용하여 단기간 부스트

(3) CPU 주위의 플랫폼이 쿨 다운에 들어가는 찬스를 포착, 터보는 보다 역동적이고 짧은 타이밍이 될 것 같다.

환경 온도의 변화에 부응, 환경 온도가 일정하다면 장기적으로 터보 상태가 계속된다. 반면 플랫폼 콜드 상태를 이용할 때는, 터보에 의해 CPU의 전력 소비가 증가, 플랫폼 자체의 온도가 상승하면 터보를 해제한다. 일시적으로 TDP를 넘어 부스트가 짧은 사이클 모드도 보인다. 예를 들어, 1 분 등 짧은 기간에 터보가 상정되고 있는 것 같다. 또한, 주파수의 향상 폭이 30여 %로 더 커진다.

이 터보 모드가 상정 할 수있는 것은 시스템의 가동률이 낮은 플랫폼이 식은 상태에서 높은 부하의 응용 프로그램을 시작한 상태 등인 것이다. 그동안 쿨했던 분의 예산을 사용하여 단기간 터보한다. 따라서 고부하 애플리케이션 응답 시간도 향상 될 것으로 생각된다.

(4) 패키지 수준의 터보도 MCM (Multi-Chip Module) 형태의 CPU로 상정 할 수있다. 이에 대해서는 Friedman 씨의 설명은 없었지만, 쉽게 추측이 가능하다.

예를 들어, Havendale / Auburndale처럼 CPU 패키지에 CPU 다이 (반도체 본체)와 GMCH 다이의 2 개가 포함되는 경우. 만약 CPU의 TDP가 25W로, 짝인 칩 TDP가 10W 인 경우, TDP는 양대의 합계이다 35W로 설정된다.

하지만 CPU가 실제로는 10W 정도 밖에 소비하지 않는 상태 일 수도 있다. 이런 경우는 짝이 되는 칩을 10W의 TDP를 넘어 성능 향상 여지가 나타난다. 반대로 짝인 칩이 5W 정도 밖에 소비하지 않을 때는 CPU 측을 부스트 할 수 있다. MCM의 한쪽 다이 전력을 체크하여 터보 모드로 전환하는 메커니즘을 짜는 것은 가능할 것이다.

물론, 두 칩의 다이 핫스팟의 온도가 "Tj (junction. = 히트스프레더와 접촉되는 다이의 온도. 인텔 CPU 스펙을 보면 히트스프레더(뚜껑)가 없는 노트북용 같은 칩은 Tj 온도가 표기되고, 데스크탑은 Tcase 온도가 적혀 있습니다. 또 예을 들면 Tj가 100도 라면 Tc는 6,7x 도 정도 됩니다. 다이에 히트스프레더가 금속으로 땜질이 되어 있고, 열전도가 높은 구리를 쓴다해도 열이 무한대의 속도로 전도되지 않기 때문에 당연히 온도 차이가 있겠죠.)"의 스펙을 초과한 경우는 열 센서가 터보를 정지되게 될 것이다. Tj가 사실상 제약이 될 것으로 추정된다. 따라서 히트 싱크나 히트 스프레더와 열전달 물질의 열 저항 값을 낮추게 되면 더욱 터보의 여지가 늘어난다.

전압 조절기의 개혁도 필요

다양한 트리거 성능을 향상하는 터보 모드. 하이파 디자인 센터는 이전부터 터보 모드를, Intel 내부에서 추진하고 있었다고 한다. 이렇게 센터의 터보 모드의 전체 구상을 듣고, 그 이유를 잘 알 수있다. 터보 모드는 일정한 냉각 능력에 따라, CPU의 성능 최적화를 도모하기위한 메커니즘으로 자리 매김하고있다.

또한, 터보 모드 제어는 다양한 발전계(보)도 생각할 수 있다. 예를 들어, 터보 동작은 핫스팟 열이 한계에 도달한 CPU 코어를, 자고 있던 있던 CPU 코어와 교대한다. CPU 코어가 8 코어 등 다수되면 이러한 동적 스왑, CPU 다이 전체의 발열을 균등화 하는 방법이 나온다.

또한 향후 각 CPU 코어에 대해 별도의 전압 공급을 실현할 수 있게 되면 (하스웰 부터 코어별로 별도 전압을 공급하죠), 터보 모드는 더 활용할 수 있다. 자고 있는 CPU 코어의 전압을 떨어 뜨리고, 더 전력 소비를 줄여 터보하는 CPU 코어의 주파수를 한층 더 끌어 올릴 수 있기 때문이다.

무엇보다, 그래서 전압 조절기의 개혁이 필요하다. 그리고 그 장애물이 높다. Friedman 씨는 다음과 같이 설명한다.

"우리가 비용 면도 고려해야 함을 기억하자. 만약 각 코어에 각각 독립된 전력 공급을 행하면 시스템의 전력 공급 비용이 뛰어 버린다. 그런데 현재는 PC 가격은 점점 낮아지고 있다. 따라서 시스템 비용과 전력 최적화의 균형을 잡아야 한다.

향후 전력 공급에 더욱 비용이 효과적인 해결책을 제공하는 경우, 각 코어에 대한 전용 전원 공급을 제공 할 것이다. 하지만 그때까지는 비용이 너무 높다. 다양한 기술이 있지만, 현재 양산에 비용이 너무 크다 "

예상되는 해결책은 2005 년의 Intel Developer Forum (IDF)에서 Intel이 보여준 CMOS 전압 레귤레이터이다. CMOS 기술로 만들어진 칩 크기의 레귤레이터를 CPU 다이 동일한 기판에 올려 전력 공급을 행한다. CMOS 전압 조정기는 여러 전압 레벨에서의 전력 공급을 저렴한 비용에 할 수 있고, 다른 전압의 전환도 매우 짧은 지연 시간으로 가능하다. 따라서 주문형 코어 단위의 전압을 조금씩 변화 할 수있다.

Intel의 Justin R. Rattner (저스틴 · R · 래트너) 씨 (Senior Fellow, Corporate Technology Group 겸 CTO, Intel)는 2005 년 IDF 때로는 다음과 같이 설명했다.

"CMOS 칩 레귤레이터를 사용하여 개별 코어 단위 뿐만 아니라, 개별 기능 블록 단위로 전력 제어가 가능하게 될 것이다. 블록마다 개별적으로 전력을 업하거나 다운. 가장 첫 번째 목적은 각 코어에 공급되는 전압을 세밀하게 전환하여 코어 단위의 조절을 효율적으로 수행하는 것이다.

멀티 코어 CPU에서의 전력 제어의 과제는 모두 함께 업 또는 다운해야 한다, 모처럼의 멀티 코어의 잠재적인 이익을 잃어 버리는 점이다. 이를 위해 전압 조절을 하고 싶다. 전압과 주파수를 코어 단위로 정밀하게 제어하는 그것이 우리의 연구 과제가 되고있다 "

CMOS 전압 레귤레이터 등의 기술이 양산 수준에서 실현 될 수 있으면, 멀티 코어의 각 CPU 코어에 자유 자재로 다른 전압에 전력을 공급할 수 있게 된다. 그것이, 터보 모드 제어와 일체가 되면, 멀티 코어 CPU의 성능은 자유롭게 최적화 할 수 있게 된다. 그러나 Friedman 씨가 지적 하듯이, 그것은 앞으로의 일이 될 것 같다. (결국 하스웰에 가서야 통합되죠.)

2005 년 IDF, 래트너 씨의 기조 강연에서 보여준 그림

[분석정보] Haswell 절전 기능의 열쇠 "FIVR" 과 그 이후

[분석정보] 평균 소비전력을 크게 줄일 Penryn의 C6 스테이트

[분석정보] 이스라엘에서 발신되는 인텔의 차세대 CPU 기술

[2000.08.25] 그래픽 통합 CPU 팀나(Timna)의 개요를 분명히-극적인 다이 크기 축소를 실현

[정보분석] 2개의 CPU 개발팀이 경쟁하는 Intel의 사내 전략

[정보분석] 같은 무렵에 시작된 Nehalem과 Larrabee와 Atom

[고전스페셜] Intel, 45nm 공정의 153Mbit SRAM 제조 성공

[분석정보] 전면 개량이 아닌 부분 개량에 머문 Penryn

'벤치리뷰·뉴스·정보 > 아키텍처·정보분석' 카테고리의 다른 글

| [분석정보] Intel이 드디어 Silverthorne과 Tukwila의 개요를 발표 (0) | 2008.02.04 |

|---|---|

| [정보분석] 2개의 CPU 개발팀이 경쟁하는 Intel의 사내 전략 (0) | 2008.01.30 |

| [분석정보] Bulldozer가 후퇴한 AMD의 로드맵의 의미 (0) | 2007.12.27 |

| [분석정보] 현실 노선으로 수정된 AMD의 FUSION (0) | 2007.12.25 |

| [분석정보] 평균 소비전력을 크게 줄일 Penryn의 C6 스테이트 (0) | 2007.12.14 |

| [분석정보] 이스라엘에서 발신되는 인텔의 차세대 CPU 기술 (0) | 2007.12.11 |

| [분석정보] AMD, 데스크탑 네이티브 쿼드코어 Phenom을 발표 (0) | 2007.11.19 |

| [분석정보] 2008년 중에 95%를 듀얼 코어로 하는 Intel CPU로드맵의 비밀 (0) | 2007.11.09 |