Larrabee에서 분할 다시 만들어진 Knights Corner

Knights Corner의 발표를 행한 George Chrysos 씨 (Senior Principal Engineer, Intel)

Intel은 고성능 컴퓨팅 (HPC)을 위한 매니 코어 아키텍처 "MIC (마이크 : Many Integrated Core)"를, "Intel Xeon Phi"브랜드로 투입한다. 그래픽 겸용이었던 Larrabee (라라비)에서 노선을 변경한 매니 코어 제품군이다. Larrabee에서 다시 결말을 내고 코드 네임은 "Knights (나이트) '제품군으로 전환했다. Larrabee 때와 마찬가지로 Xeon 계의 Intel CPU 및 PCI Express를 통해 연결한 이기종 구성으로 사용하는 것을 전제로 한 보조 프로세서가 된다.

Intel은 Knights 제 1단으로 "Knights Ferry (나이츠 페리)"라는 32 코어의 매니 코어 CPU를 일부 연구 센터 등에 제공했다. 드디어 정식 버전인 'Knights Corner (나이츠 코너) "를 등장 시키려 한다. Knights Ferry 칩 "Aubrey Isle '은 45nm 공정 이었지만, Knights Corner는 22nm로 전환하는 것으로, 코어 수를 50코어 이상으로 늘린다.

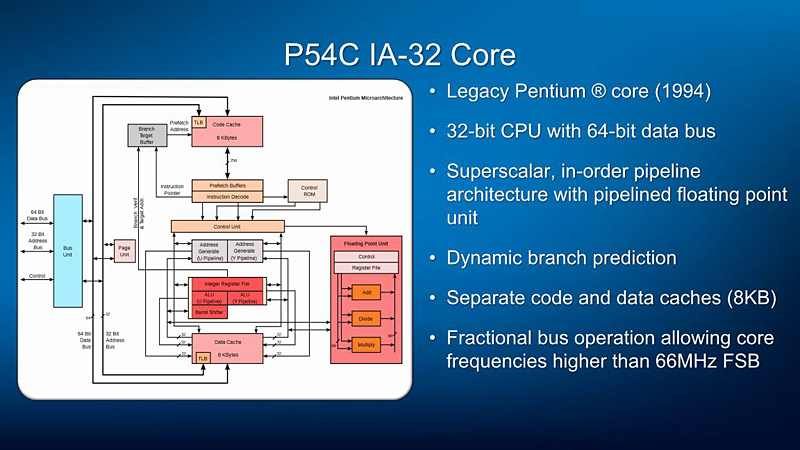

Intel은 8월 27일 ~ 29일까지 미국 쿠퍼티노 (Cupertino)에서 개최된 Hot Chips에서 Knights Corner의 개요를 분명히 했다. Knights Corner의 모습은 Larrabee와 매우 비슷하다. 다시 결론을 낸 Larrabee라고 불러도 좋을듯한 모습이다. 간단한 x86 CPU 코어 512-bit 폭의 벡터 유닛을 장착한 소형 코어 링 버스로 연결 한 구조이다. PCI Express 보드로 제공되며, 온보드 GDDR5 메모리가 탑재되어있다.

Knights Corner 개요

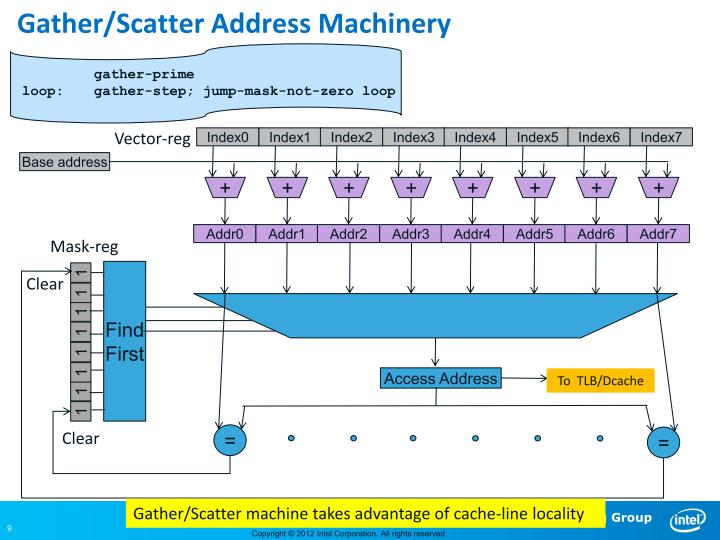

코어의 내부는 2 파이프 구성으로, 듀얼 이슈 스칼라 CPU에 벡터 유닛을 추가 한 구성으로 되어 있다. 이 점도 Larrabee와 비슷하다. 512-bit 폭의 벡터 유닛은 16-way 단 정밀도 부동 소수점 SIMD (Single Instruction Stream, Multiple Data Stream) 단위로 ,8-way 배정밀도 부동 소수점 SIMD 유닛으로 작동한다. 마스크 레지스터를 가지고 마스크를 사용한 분산 / 수집 작업 등도 있다.

코어의 내부

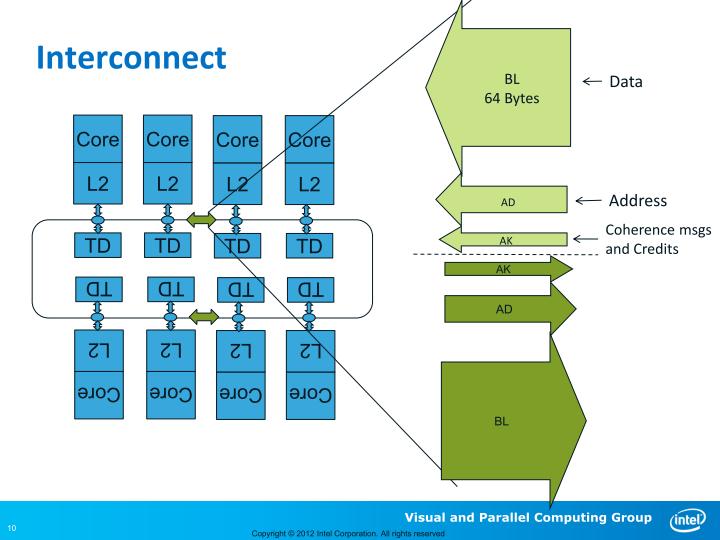

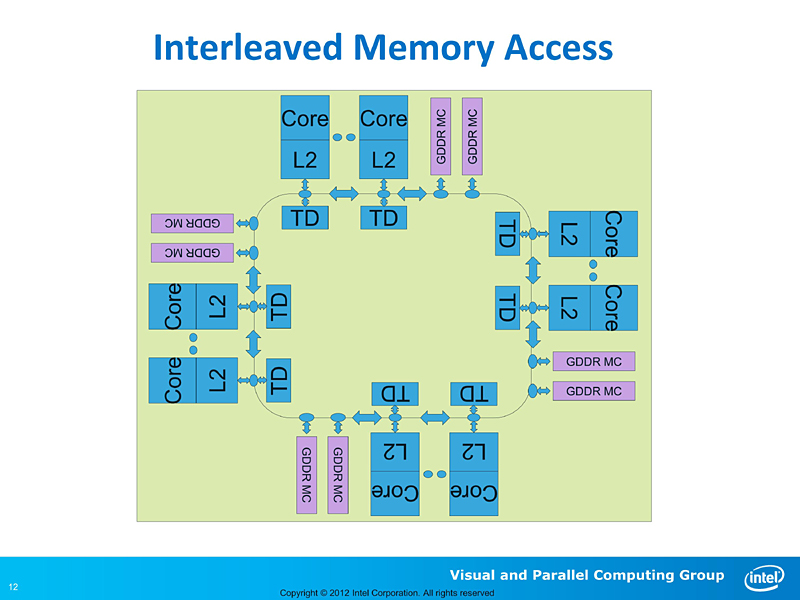

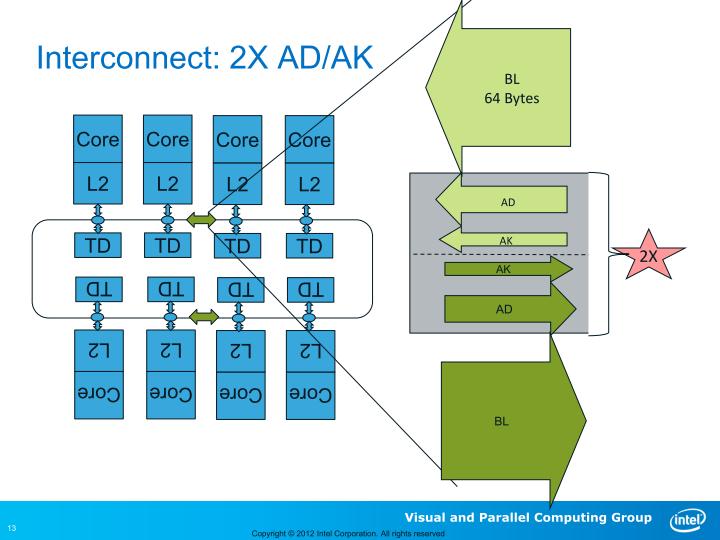

링 버스는 단방향 64bytes (512bits)의 양방향 링으로, 주소 및 일관성의 메시지 버스를 따로 가지고 있다. 그러나 Knights Corner에서 링 버스가 이 그림과 같은 구성 여부는 알려져 있지 않다. L2 캐시의 태그 집중 방식이 아닌 태그 디렉토리가 각 각 CPU 코어와 L2 슬라이스 쌍을 포함하고 있다. L2 캐시의 크기는 Larrabee의 256KB에서 두배로 512KB가 되었다.

내부 인터커넥트

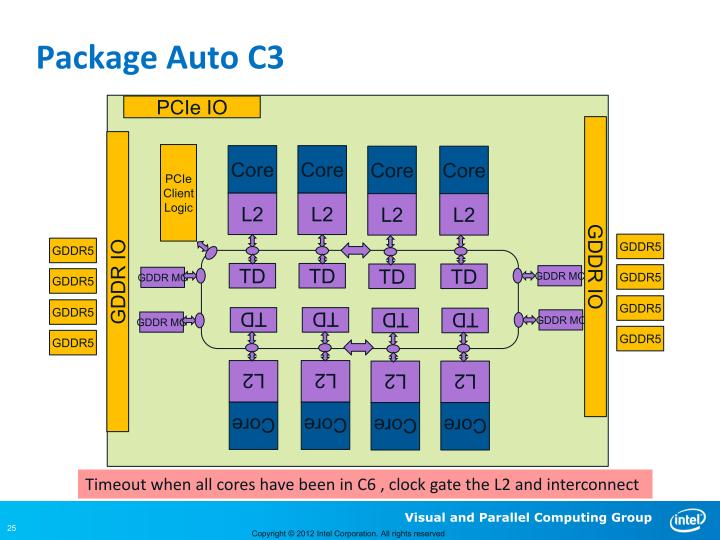

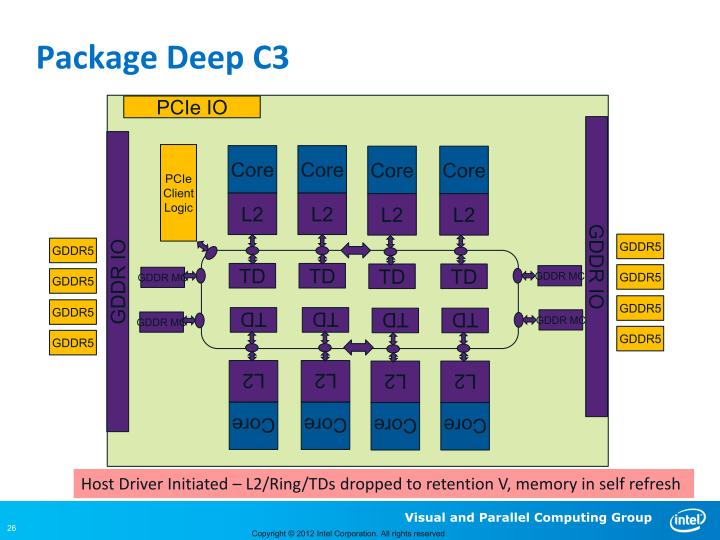

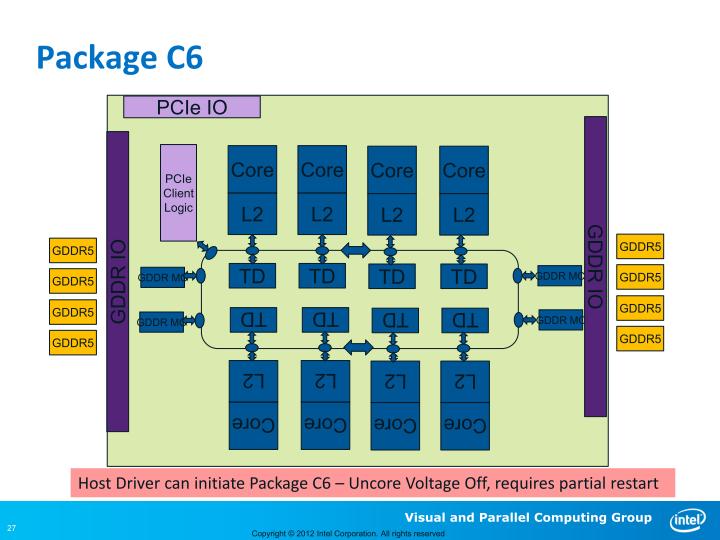

Larrabee1에서 큰 문제가 된 소비 전력도 Intel의 자랑으로 절전 제어를 담은 것으로 개선되었다. 이번 칩은 코어 단위의 파워 게이팅 (CC6) 스테이트에서 전체 칩에서 파워 게이팅 (Package C6)까지 단계적으로 전력 제어가 이루어진다. Intel은 Knights Corner는 파워 성능에서 NVIDIA와 AMD의 GPU 기반 이기종 (Heterogeneous : 이종 혼합) 구성에 필적 할 수 있다고 말한다.

소비 전력 개선

스마트폰을 노리는 Atom 기반 SoC Medfield

Medfield의 발표를 행한 Intel의 Rumi Zahir 씨

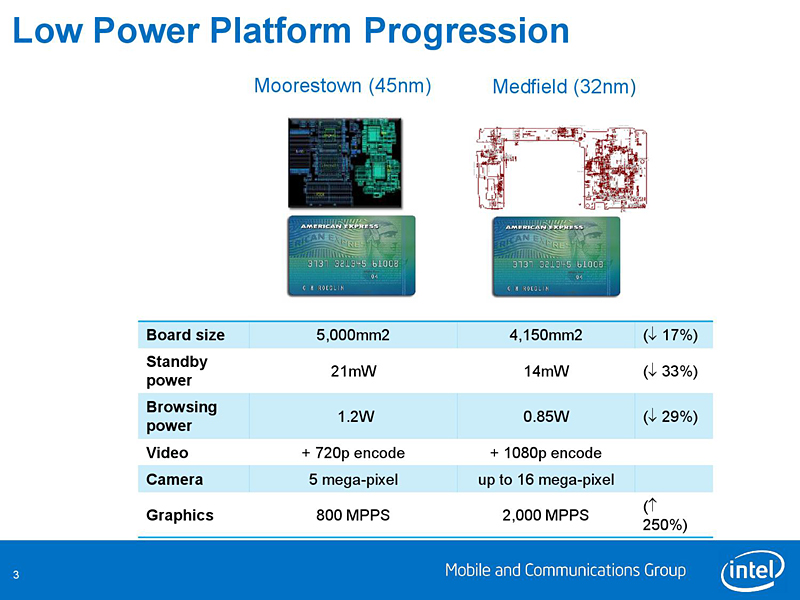

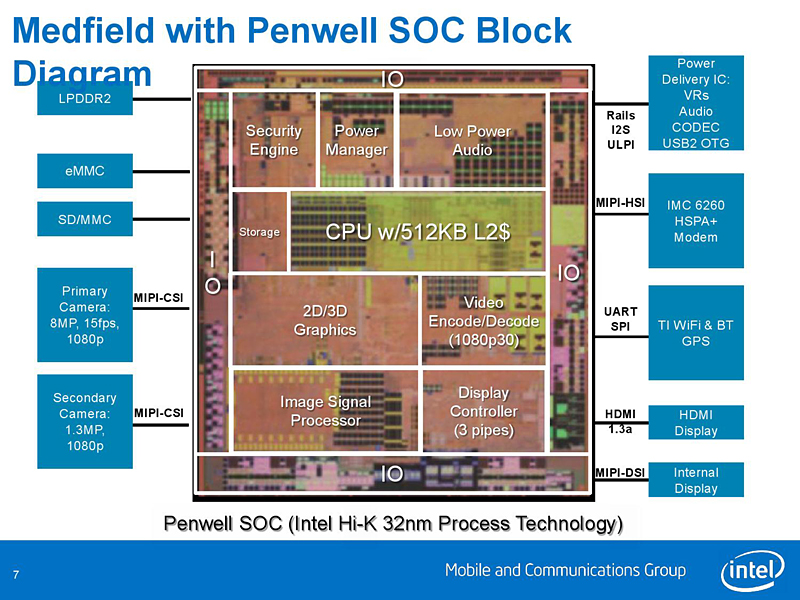

Intel은 Hot Chips에서 HPC를 위한 Knights Corner 와는 정반대의 모바일 장치용 Atom SoC (System on a Chip) 인 'Medfield (메드필드) "의 개요를 밝혔다. Medfield는 "Atom Z2460 '의 제품명으로 출시되고 있다. CPU 코어는 싱글 코어의 32nm 버전 Atom 코어 "Saltwell (솔트웰)"GPU 코어는 "PowerVR SGX540"2 채널 (2x32)의 LPDDR2을 갖춘 32nm 공정으로 제조된다. 칩 자체의 코드 네임은 "Penwell (펜웰) '로 Medfield는 플랫폼의 코드 네임이다. Intel이 Medfield 세대에서 Atom 스마트폰을 본격적으로 노린다.

Medfield 개요

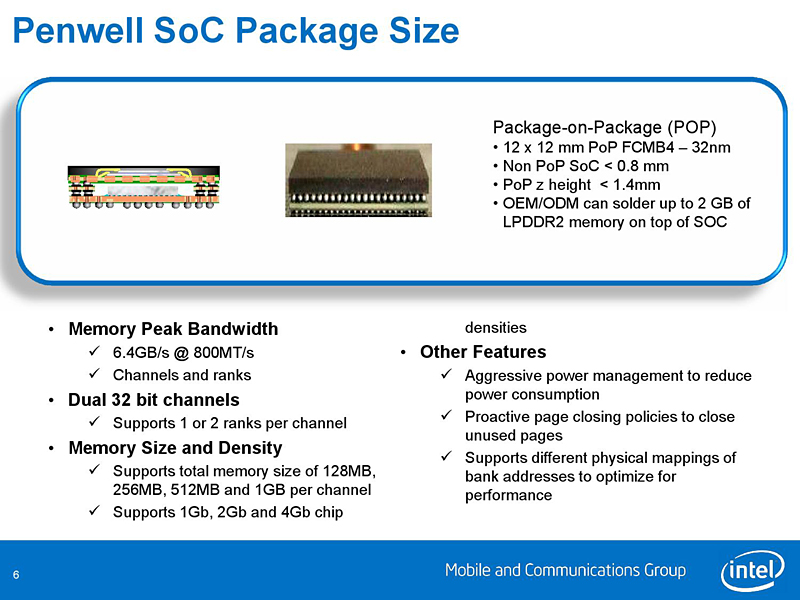

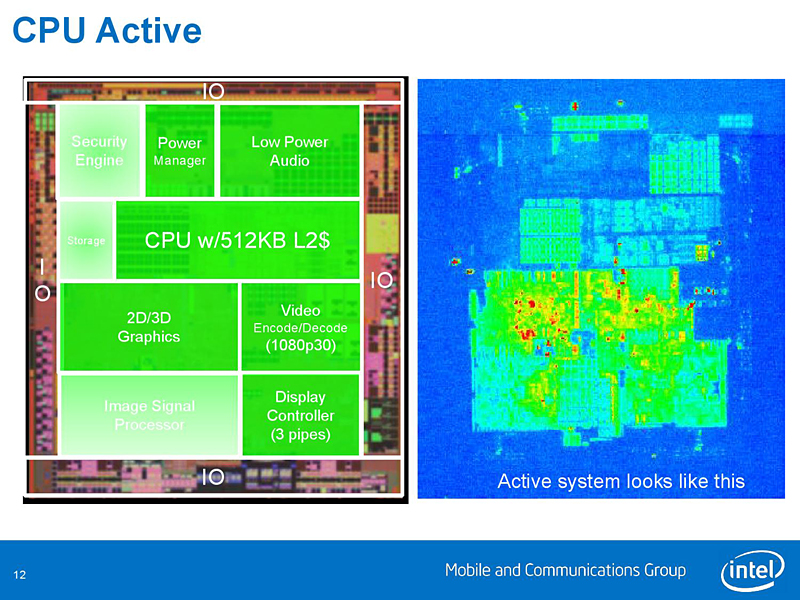

Hot Chips에서는 희미하지만 Medfield의 다이 레이아웃이 밝혀졌다. I / O를 제외한 다이의 절반이 그래픽 관련이 차지하고 있는 것을 알 수 있다. 또한 패키지는 모바일 시장에서 요구되는 "Package-on-Package (POP)"옵션이 있다는 것도 밝혀졌다. 최대 2GB까지 LPDDR2를 POP 패키지에 담을 수 있다.

Medfield의 다이 레이아웃

POP 옵션 Medfield

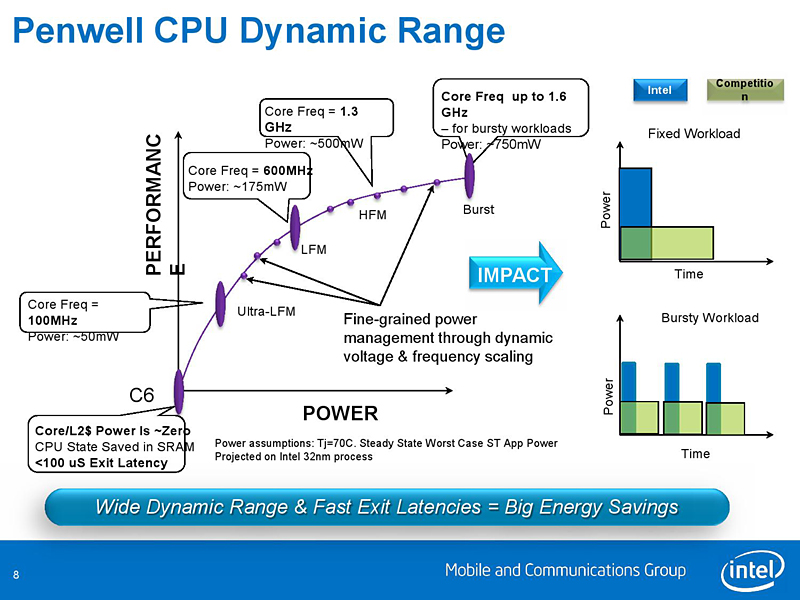

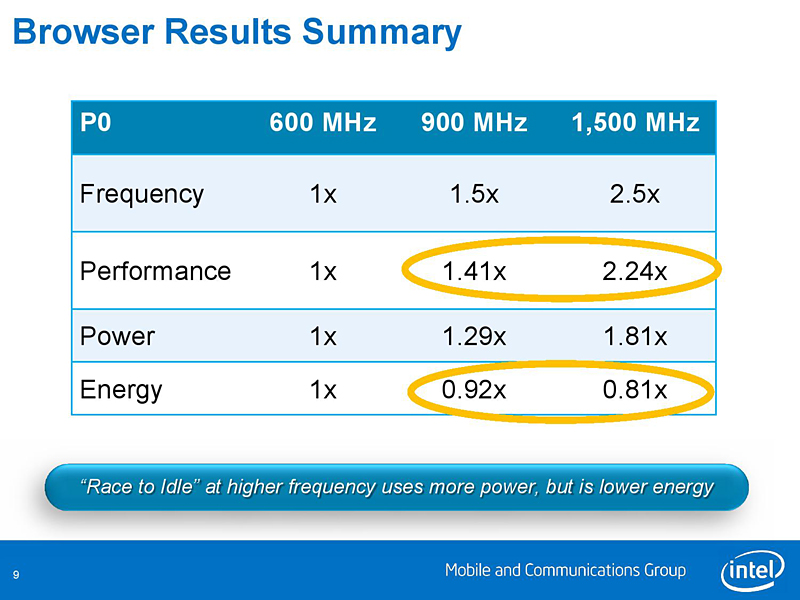

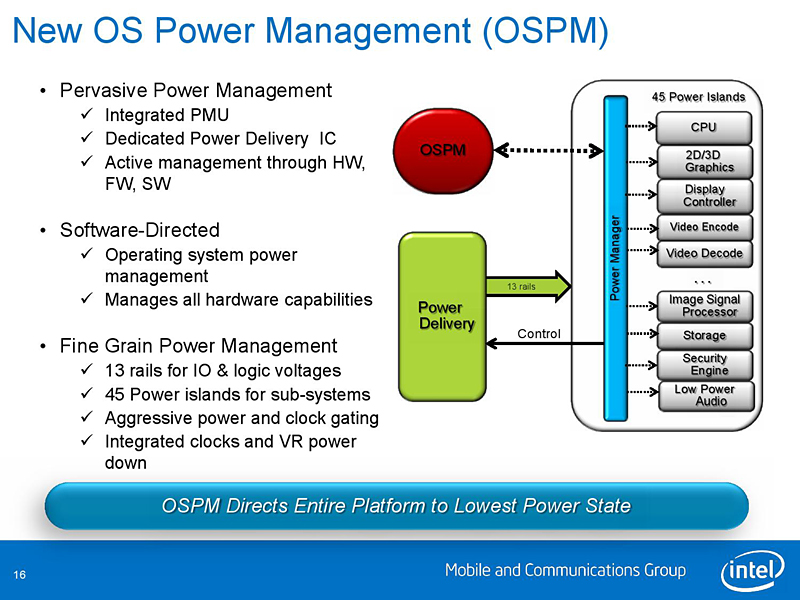

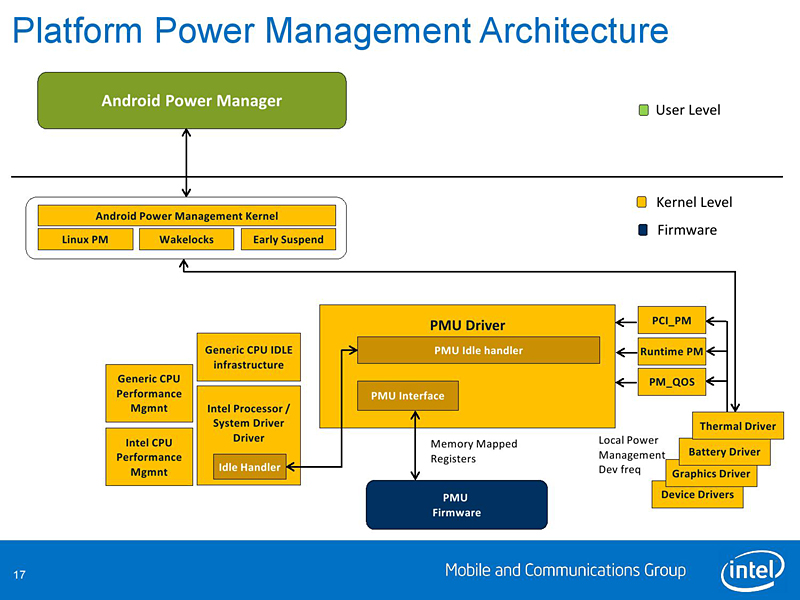

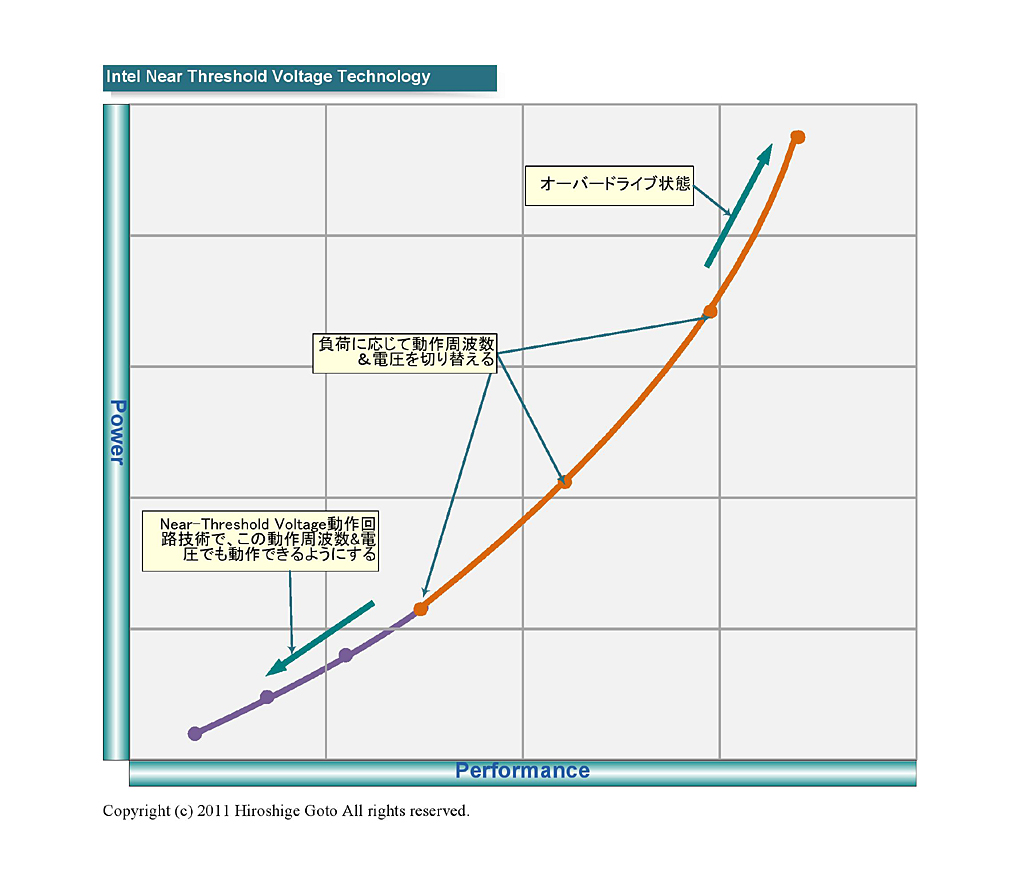

전력 제어는 부하에 따라 전압과 동작 주파수를 전환 "DVFS (Dynamic Voltage and Frequency Scaling) '을 섬세한 단계로 행한다. 100MHz에서 1.6GHz까지의 범위에서 움직이는 것이 가능하다. 높은 주파수에서 빨리 작업을 끝내는 것으로, 빠른 아이들 상태로 전력 소비를 억제하는 발상이다.

전력 제어 및 클럭 주파수

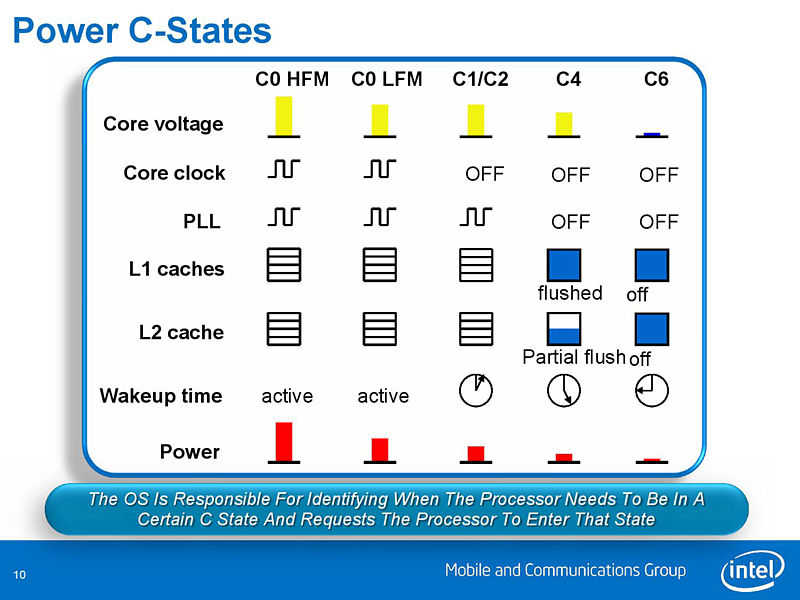

또한 전력 제어는 기존의 CPU에서 행해 온 C6의 파워 게이팅까지 제어 외에, SoC 전체에 전력 제어로 새로운 "S"수준의 스테이트가 설정되었

다. CPU 코어 이외의 장치를 파워 게이트하고 LPDDR을 셀프 리프레쉬 하는 SOi1과 완전히 해제 SOi3이 새롭게 마련됐다.

C 상태 전환

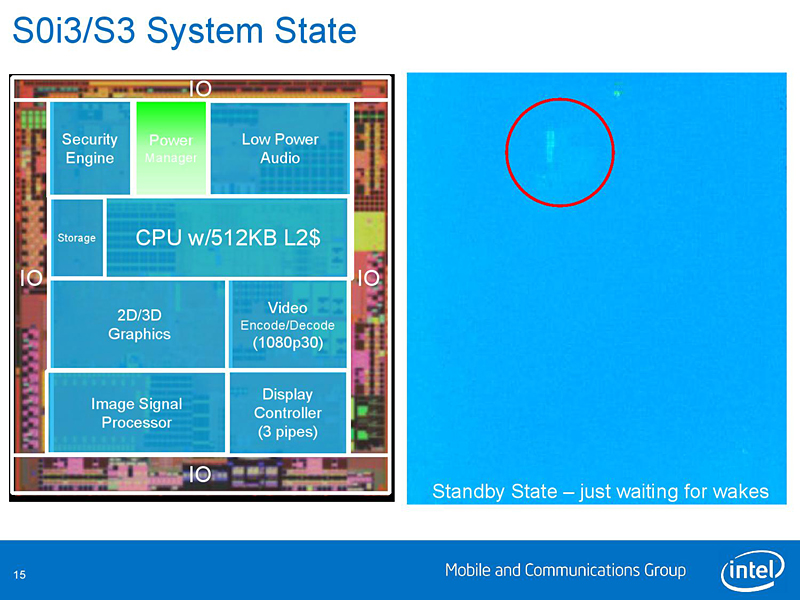

전체 시스템은 비 CPU 코어 부분이 대부분이고, 게다가 그래픽은 전력을 소비하기 때문에 SoC 전체 전력 제어의 효과는 크다. SOi3 상태에서는 전력 관리 유닛 부분만 작동하고 있을 뿐이다.

SoC 전체 전력 제어

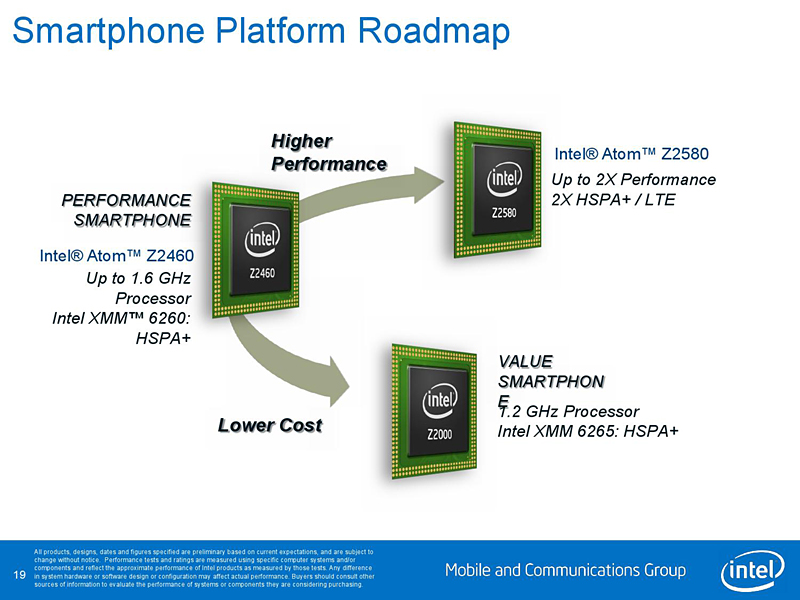

이러한 SoC 형식의 절전 기능의 도입에 따라 OS 측에 대한 전원 관리 API도 확장된다. 이렇게 뜯어보면 Medfield는 스마트폰에 최적화 된 SoC가 된 것을 알 수있다. 사실, 선행하는 ARM 기반의 스마트폰 SoC에 한바퀴 늦음에서 따라잡은 단계이지만, Intel은 염원의 모바일 시장 공략에 이 Medfield 로 본격적으로 들어간다. Z2460 이후, 2 배 성능 "Atom Z2580 '와 저가"Atom Z2000'이 이어진다.(2배 성능이란건 2코어 제품을 말하는 겁니다.)

스마트 폰의 SoC가 된 Medfield

Ivy Bridge 제품군의 절전 기술

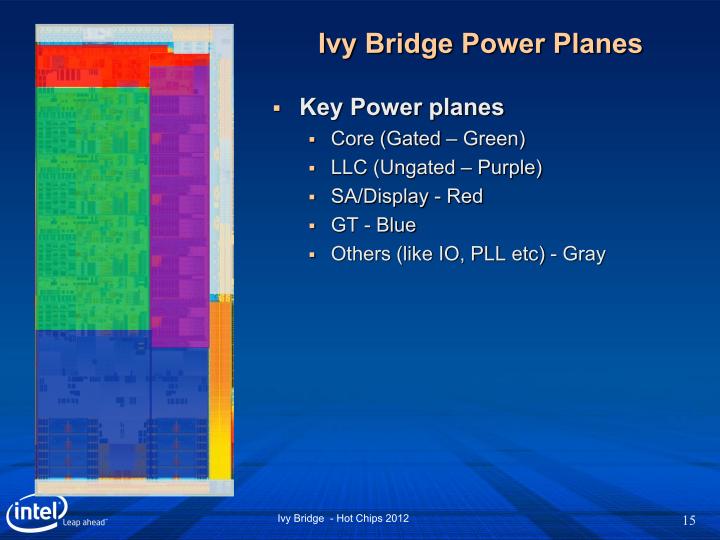

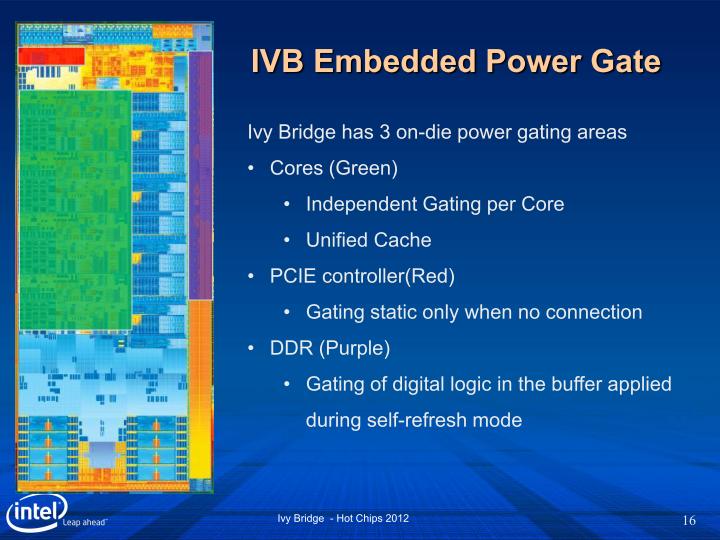

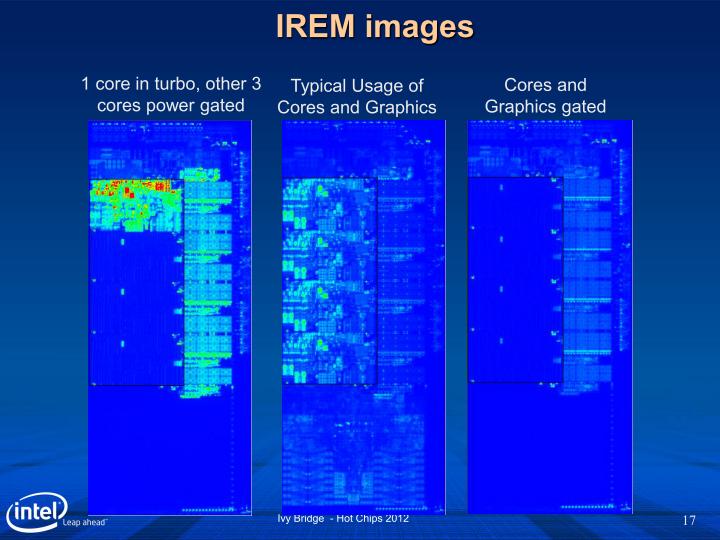

Intel은 이 밖에 Hot Chips에서 "Ivy Bridge (아이비 브릿지)"제품군의 전력 제어에 대해서도 발표를 했다. Ivy Bridge의 파워 플레인은 아래의 그림과 같이 녹색의 CPU 코어 부분과 보라색의 LL (Last Level) 캐시 부분, 빨간 노스 브릿지 부분과 파란색의 GPU 코어 부분, 그리고 회색 나머지 부분으로 나누어 져있다. 기본은 지금까지의 Sandy Bridge (샌디 브릿지)와 같지만, Ivy Bridge는 전력 제어는 더 확장되어 DDR 메모리 I / O도 파워 게이팅 된다.

Ivy Bridge의 전력 제어

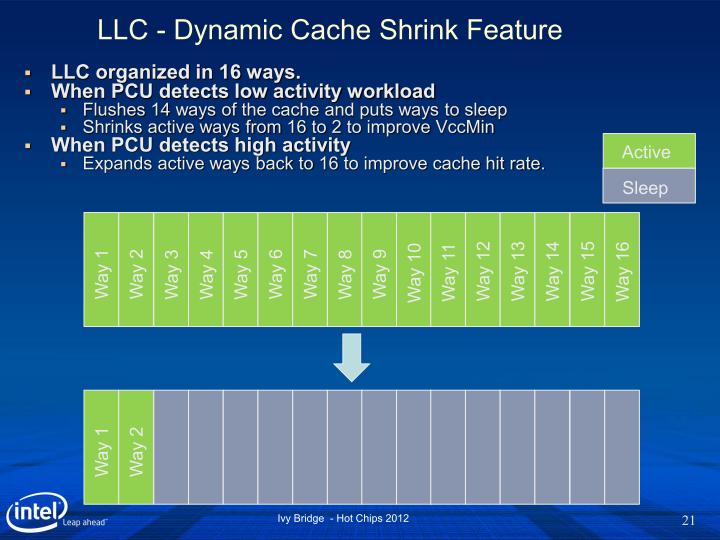

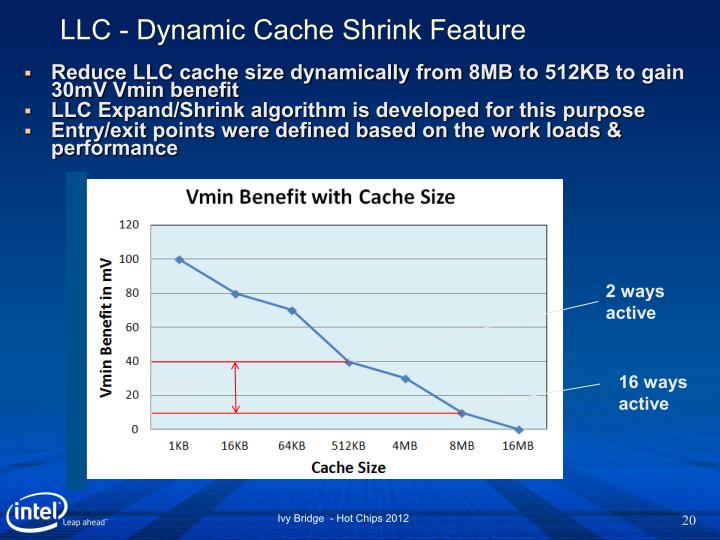

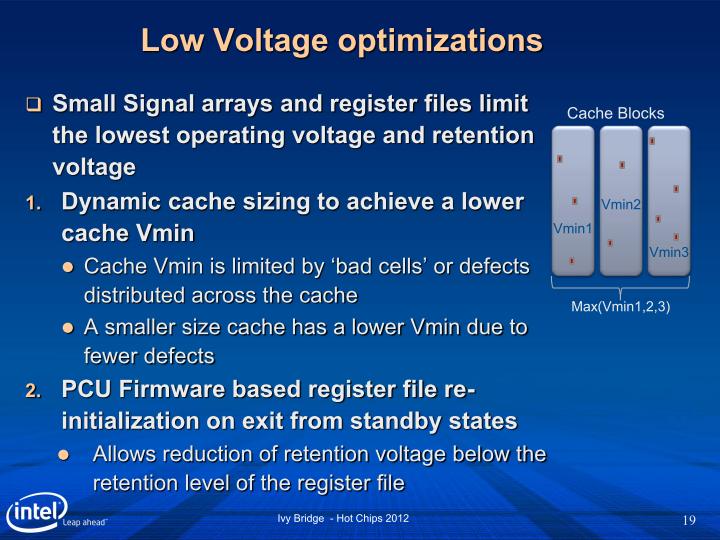

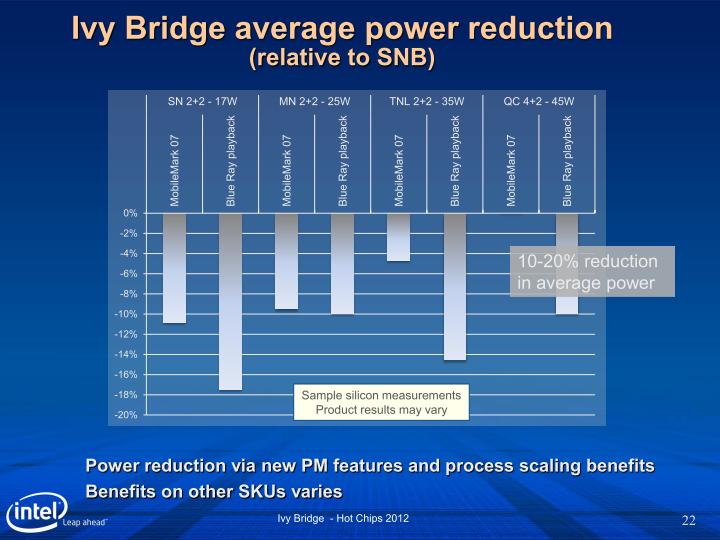

Ivy Bridge의 LL (Last Level) 캐시는 16way로 Way 단위로 슬립 할 수있다. 이때, LL 캐시 활성 way를 줄일수록 캐시 부분의 전압을 낮춘다. 이것은 활성 캐시 블록이 적어지면 전압을 낮추는 경우에 장해가 되는 저전압시 데이터를 유지할 수 없는 셀이 블록에 포함될 가능성이 줄어들기 때문 이라고 한다. 이러한 섬세한 전력 절약 화에 의해, Ivy Bridge는 Sandy Bridge보다 평균 전력 소비가 내려간다.

LL 캐시 구조

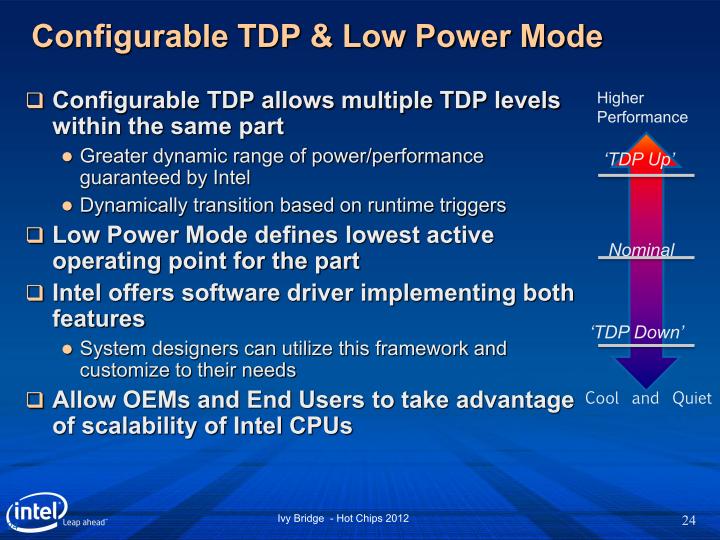

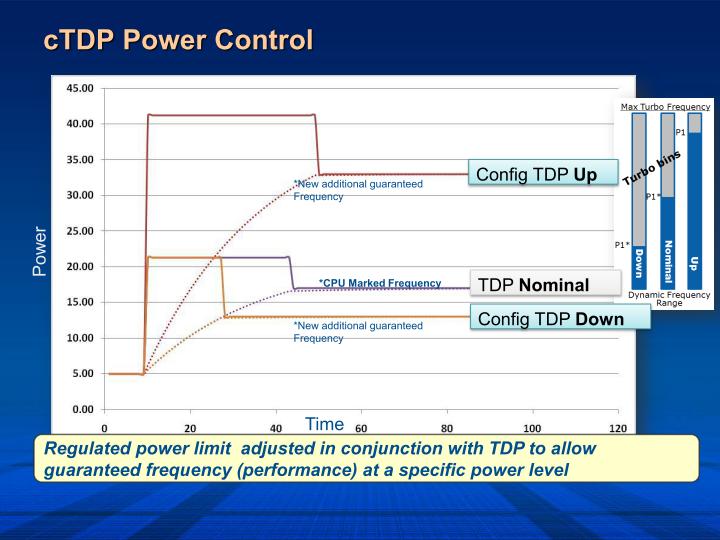

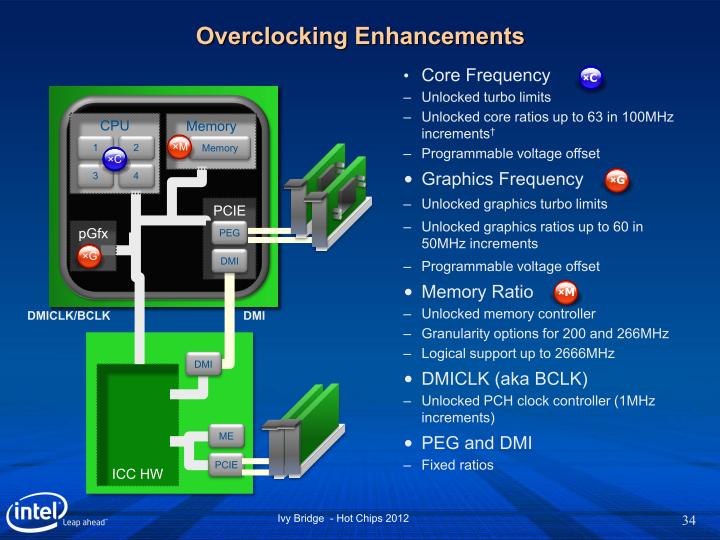

또한 Hot Chips 에서는 Ivy Bridge의 컨피규러블 TDP (Thermal Design Power : 열 설계 전력)에 대해서도 설명했다. 이것은 이미 Intel Developer Forum (IDF) 등 에서 설명되어 있지만, 동적으로 TDP를 변화시키는 기술이다. 기존의 TDP 형편에 의한 것에서 별도로 넘는 시스템 설계가 가능하게 된다. 예를 들어, 노트북 PC에 폐열기구를 갖춘 도크 스테이션을 연결하여 높은 TDP를 다시 설정하는 것이 가능하다. 또한 오버 클러킹 기능에 대해서도 언급했다.

컨피규러블 TDP

Intel의 비장의 카드인 기술 Near-Threshold Voltage

Hot Chips에서는 이 밖에 Intel은 Xeon Processor E5 (Sandy Bridge-EP) 제품군의 버스 아키텍처 및 전력 제어 등에 대해 강연을 했다. 또한 Intel의 기술 중 가장 주목을 받고 있는 근 임계 전압 (Near-Threshold Voltage : NTV) 회로 기술에 대해서도 세션이 열렸다.

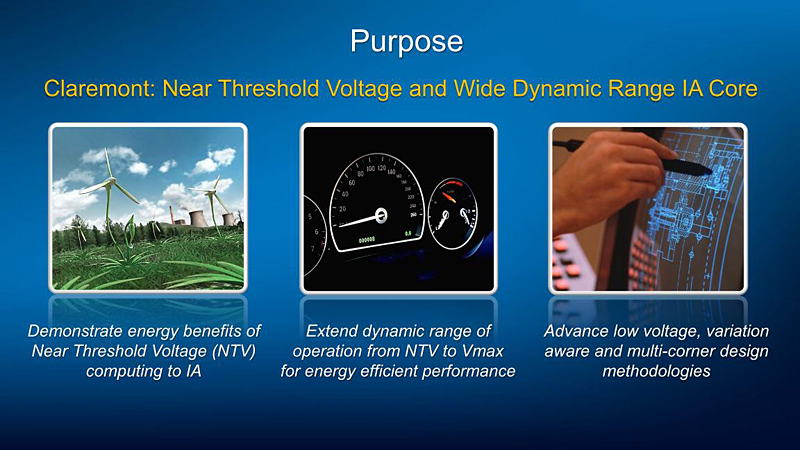

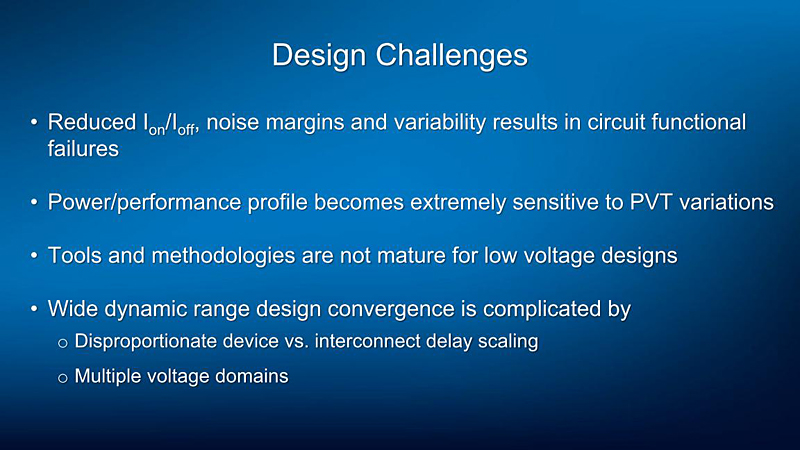

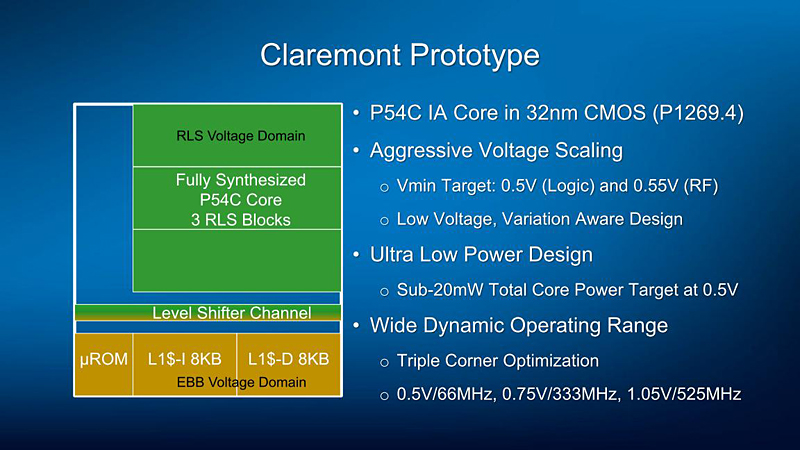

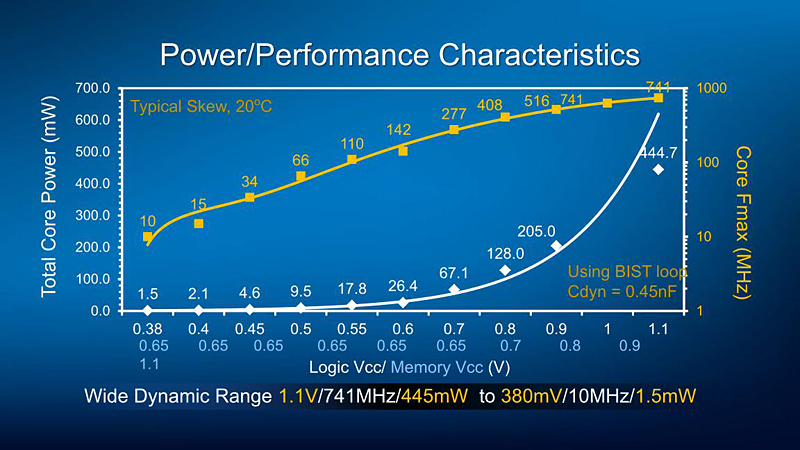

Intel은 초 저전압 동작을 가능하게 하는 이 Near-Threshold Voltage 기술을 미래의 전력 제어 카드로 하는 생각으로 적극적으로 개발하고 있다. 현재는 32nm 공정에서 NTV 기술을 사용한 CPU를 몰래(순 일본식 표현이라 딱히 뭐라고 해야할지;;) 시험제작, 작동 시험을 진행하고 있다. Hot Chips에서는 시제품 칩 "Claremont"의 개요를 발표했다. Claremont 대상은 0.5V에서 66MHz 로 20mW의 동작을 가능하게 하는 것으로, 1.05V시 525MHz 매우 넓은 동작 주파수 및 전압 범위를 갖는다.

Near-Threshold Voltage 기술

Intel의 파워 성능 전략

2012년 8월 31일 기사 입니다.

[분석정보] 전환기를 맞이한 2014년 인텔의 서버 프로세서

[분석정보] 스몰 코어 CPU Avoton '에서 밝혀진 Intel의 저전력 CPU 전략

[분석정보] Intel, 14nm SoC 버전 Broadwell / Denverton 절전 서버 출시

[분석정보] 스몰 코어 마이크로 서버로 기우는 Intel의 서버 전략

[분석정보] 매니코어 프로세서로 손바닥 슈퍼 컴퓨터를 실현

[분석정보] 2012년 vPro는 클라이언트 관리의 결정적 수단이 되는가? 1/2부

[분석정보] 2012년 vPro는 클라이언트 관리의 결정적 수단이 되는가? 2/2부

[분석정보] 아이테니엄(Itanium)을 둘러싼 불안과 기대

[분석정보] Intel 매니코어 MIC 와 Atom SoC Medfield 를 발표

[분석정보] 2013년에 출시되는 Intel의 새로운 서버용 프로세서

[분석정보] Intel, HPC 전용 보조 프로세서 Xeon Phi 2013년 1월부터 일반용으로 출시

[분석정보] IDF 2012에서 주목한 한가지, 매니 코어 "Knights Corner"

[정보분석] 엔비디아 세계 최다 트렌지스터 칩 GK 110 공개

[정보분석] IDF 2011 Justin Rattner 기조연설 매니코어 시대가 다가옴 1/2부

[정보분석] IDF 2011 Justin Rattner 기조연설 매니코어 시대가 다가옴 2/2부

[정보분석] 같은 무렵에 시작된 Nehalem과 Larrabee와 Atom

[분석정보] Intel은 Larrabee 계획과 아키텍처를 어떻게 바꾸나?

[분석정보] 다시 처음부터 시작된 라라비 무엇이 문제였나?

[분석정보] 라라비 (Larrabee)의 비장의 카드 공유 가상 메모리

[분석정보] 인텔의 스칼라 CPU + 라라비의 이기종 CPU 비전

[분석정보] Larrabee는 SIMD와 MIMD의 균형 - Intel CTO가 말한다.

[정보분석](암달의 법칙) 2010년대 100 코어 CPU 시대를 향해서 달리는 CPU 제조사

[분석정보] GDC 2009 드디어 소프트 개발자 정보도 나온 "Larrabee"

[정보분석] Intel 힐스보로가 개발하는 CPU 아키텍처의 방향성

[정보분석] 팀스위니 미래의 게임 개발 기술. 소프트웨어 렌더링으로 회귀

[아키텍처] 베일을 벗은 인텔 CPU & GPU 하이브리드 라라비(Larrabee)

[정보분석] 암달의 법칙(Amdahl's law)을 둘러싼 Intel과 AMD의 싸움

[정보분석] 모든 CPU는 멀티 스레드로, 명확하게 된 CPU의 방향

'벤치리뷰·뉴스·정보 > 아키텍처·정보분석' 카테고리의 다른 글

| [분석정보] IDF 2012. 22nm 세대에서 14nm 세대로 이행하는 Intel의 실리콘 제조 기술 (0) | 2012.09.14 |

|---|---|

| [아키텍처] 차세대 CPU "Haswell"(하스웰) 의 2배 강력한 GPU 코어 (0) | 2012.09.14 |

| [아키텍처] IDF 2012에서 주목한 한가지, 매니 코어 "Knights Corner" (0) | 2012.09.11 |

| [분석정보] 인텔(Intel)의 스마트폰 시장 공략 비장의 카드 Medfield (메드필드) (0) | 2012.09.07 |

| [분석정보] 모바일 SoC에서 다크 실리콘의 속박 (0) | 2012.07.26 |

| [분석정보] Research @ Intel 2012 리포트 (0) | 2012.06.27 |

| [정보분석] 엔비디아 세계 최다 트렌지스터 칩 GK 110 공개 (0) | 2012.05.19 |

| [분석정보] Ivy Bridge의 강화 포인트는 GPU 아키텍처의 개혁 (0) | 2012.04.27 |