Intel CPU의 역사를 새로 쓴 Pentium

Intel의 "Pentium (P5)"'프로세서가 등장으로부터 올해(2014년)로 20 주년이 된다. 정식 발표된 것은 1993년으로, 보급판이 등장한 것은 1994년이다. Pentium은 발표 당시 CPU 업계에 큰 충격을 주었다. 기술의 흐름을 바꿨기 때문이다. Intel에 있어서 전환점이 되었을뿐만 아니라, CPU의 역사를 새로 썼다고 말해도 좋다. (펜티엄 20주년 기념판이 K모델처럼 배수락이 해제된 하스웰 펜티엄 G3258)

초대 Pentium (P5)의 다이

그 당시는 Intel의 x86으로 대표되는 "CISC (Complex Instruction Set Computer : 복잡 명령 세트 컴퓨터)"계의 명령 세트 아키텍처 (ISA : Instruction Set Architecture)와 MIPS나 PowerPC 등의 "RISC (Reduced Instruction Set Computer : 축소 명령 세트 컴퓨터) "계 ISA 사이의 논쟁이 있었다. 간단히 말하면, CISC는 고속화가 어렵기 때문에 RISC로 대체 된다는 것이었다. 지금은 어리석다 생각되지만, 당시는 CISC 계 CPU로는 IPC (Instruction-per-Clock)는 1 또는 1 이상으로 할 수 없는, 즉 1 클럭에 평균 1 명령을 실행할 수 없다고 말했다. 따라서 성능을 올릴 여지가 큰 RISC계 CPU로 PC를 만든다는 구상이 부상하고, Microsoft도 Windows NT를 RISC에 적극적으로 올렸다. (서버나 특정 작업용 컴퓨터가 아닌 개인용 컴퓨터 PC로 가는 단계. RISC CPU NT 워크스테이션이 성공하면, NT 계로 통합되는 다음 윈도우에서 개인용으로도 잘 쓰이겠죠.)

1988년 9월 27일 기사 인텔사 반도체 시장 석권 채비

1993년 1월 16 한겨레 기사 주목받는 기술품 디지털사 64bit PC

1993년 7월 4일 경향신문 64비트급 고성능PC 나왔다

1993년 12월 8일 명령어 축약형 컴퓨터시대 활짝 CPU 혁명

1993년 12월 3일 매일경제 하이테크 혁명 컴퓨터 기술의 고도화

그러나, 인텔은 펜티엄에서, RISC의 대표적인 고속화 수법의 하나인 슈퍼 스칼라를 채용. 1 클럭에 최대 2 명령어를 실행할 수 있도록 하여, CISC 명령어 세트의 CPU에서도 하드웨어로 고속화 가능한 것을 입증했다. Pentium의 성공이 그 후 이어져, 슈퍼 스칼라 & 슈퍼 파이프 라인의 (& 아웃 오브 오더) Pentium Pro (P6)나 Pentium 4 (Willamette : 윌라멧)의 길을 열었다. 그 배후에서 RISC 계 CPU로 Windows PC를 만든다는 구상은 후퇴했다. 지금은 최고 성능의 클라이언트 CPU는 x86 계 이지만, 그 흐름을 만든 것은 Pentium 이었다.

1992년 12월 8일 매일경재 기사 컴퓨터 기술혁신 끝이 없다

1993년 12월 31일 경향신문 기사 올 최우수 컴퓨터부품 '펜티엄칩'

Pentium은 Intel의 CPU 개발 태세도 확립했다. 2년에 1번, 로직 공정 기술을 미세화하고, 2년마다 새로운 CPU 아키텍처를 도입한다 (2팀 개발). Intel의 이 CPU 전략이 시작된 것은 Pentium부터로, 그 이전은 4년에 한번 아키텍처를 갱신했다 (1팀). 신속한 개발을 위해 Intel은 Pentium 부터 내부적인 설계 태세를 바꿔서, 신속한 설계가 가능한 CAD 도구 등도 정돈했다.

Pentium (P5)는 한층 짧은 벡터 연산 기술인 MMX를 탑재한 "Pentium MMX (Pentium Processor with MMX Technology)"로 파생. 임베디드 버전도 만들어졌다. 뿐만 아니라 Pentium 기초 설계는, 그 후인 Intel의 다양한 CPU에도 사용되고 있다. 프로젝트가 중단된 GPU 대항의 매니 코어 CPU "Larrabee (라라비)"와 그 후계인 "Xeon Phi" 시리즈는 최신 Knights Landing 이외는 Pentium 코어를 사용했다. Intel의 연구 CPU 프로젝트에서도 Pentium 계 CPU 코어는 몇번이나 사용되었다.

Pentium은 또한 매우 성능/전력 효율이 높은 CPU 코어이기도 하다. Pentium Pro 이상의 CPU 코어는, CPU 명령의 순서를 바꿔 넣어 실행하는 아웃 오브 오더 (Out-of-Order) 실행을 채용했기 때문에, IPC는 높아졌지만, 전력 당 성능 효율은 떨어졌다. 그것에 비해 간단하게 명령을 순차적으로 실행하는 인 오더 (In-Order) 실행 스타일이기 때문에 원리 적으로는 효율이 높다. 따라서 전력 효율이 중시되고, 임베디드로의 대응이 중요해진 20 년 후인 지금도, Pentium 계의 CPU 코어 설계는 다시 재검토되고 있다.

486에서 아키텍처를 크게 발전시킨 Pentium

Intel은 4004로 세계 최초의 마이크로 컴퓨터를 발표한 이래, MPU (CPU)를 진화시켜 왔다. 16-bit 8086은 널리 채용되어 PC 시대의 기초를 쌓았다 (8088은 8086의 보급형). 그 후는 "80286 (286)"을 거쳐서 "386 (80386)"에서는 x86 명령을 32-bit로 확장했다. 386 명령어 페치 (인출) -> 명령 디코드 -> 명령 실행의 간단한 3 스테이지 파이프 라인 구성이었다.

이어 486 계는 386을 기반으로 철저한 고속화를 도모했다. 파이프 라인 스테이지를 5 단으로 깊게해서 고클럭화를 쉽게했다. 부동 소수점 (FP) 유닛을 더하고, 명령과 데이터를 위한 캐시를 탑재했다. 486에서는 간단한 명령은 1 클럭에 1 명령 처리량으로 실행하는 것이 가능했다. (CISC CPU는 RISC CPU의 2~3명령에 해당하는 복잡명령도 있기 때문에, 486은 약 0.55의 클럭당 명령 처리.)

386에서 Pentium MMX (P55C)까지의 아키텍처 전환.

(486에서도 초기형은 8kB 캐시, 펜티엄이 나온 이후의 후기형 486 DX4는 16kB 캐시. 캐시 방식도 초기형은 라이트 스루, 후기형은 라이트 백 방식.)

[분석정보] CPU와 메모리의 속도 차이를 해소하는 캐시의 기초지식

Pentium은 그 486부터 한층 고속화를 노리고 설계되었다. 주목적은 우선 정수 연산 실행 파이프를 2개로하여, 최대 2 명령을 동시에 실행할 수 있도록 한 것. 이를 위해 명령 디코더도 2-way로 2 명령을 동시 디코딩 할 수 있도록 했다. 486까지는 1 사이클에 최대 1 명령 디코드로 최대 1 명령 실행이었다. 또 486에서는 통합된 캐시는 명령과 데이터로 분리. 조건 분기에 의해서 파이프 라인 실행이 흐트러지는 것을 막기 위해 분기 예측기구도 탑재했다. FP 유닛도 파이프라인화 하고 1 명령 1사이클 처리량으로 실행 할 수 있도록 했다.

좀 더 자세히 보면 Pentium (P5)는 8KB의 L1 명령 캐시를 갖고, 분기 예측은 분기 상태와 분기 앞쪽의 주소를 캐시하는 "Branch Target Buffer (BTB)"을 갖춘다. 조건 분기 명령이있으면, 그 명령의 뒤에 오는 명령 흐름은 분기가 확정 될 때까지 기다리지 않으면 안된다. 분기 예측은 분기가 성립하는지 아닌지를 예측해서, 분기했을 경우 건너뛰어 앞쪽의 주소를 예측하는 것으로, 조건 분기 명령을 따르는 명령을 투기적으로 수행 할 수 있도록 하는 기구이다. Pentium은 파이프 라인이 386 시대보다 깊어져 2 명령 실행 되었기 때문에 조건 분기에 의한 손실이 커졌다. 분기 예측은 그것을 커버하기 위해 구현되었다.

초대 Pentium (P5)의 마이크로 아키텍처

x86 CPU에서는 처음으로 2 파이프 라인의 정수 연산 유닛

Pentium은 인 오더 실행 CPU이기 때문에, 2명령 실행이라고 말해도, 연속하는 2개의 명령만 동시에 실행할 수 있다. 또 실행 가능한 명령의 조합에는 제약이 있다. 의존성이없는 "단순"명령 만이 쌍으로 실행 가능하다. 단순 명령은 레지스터 간 연산이나 메모리에서 데이터를 로드 / 스토어 등. 연산과 메모리 액세스가 복합된 명령은 쌍으로 실행할 수 없다. 또, 선두의 명령이 점프 명령인 경우에도 다음의 명령은 동시에 실행할 수 없다. 또 두 번째 명령이 첫 번째 명령이 고쳐쓴 레지스터를 참조 혹은 고쳐스는 경우도 쌍으로 실행할 수 없다.

Pentium (P5)는 2 파이프로 병렬 실행을 하기 때문에 486보다 클럭 당 성능이 높다

실행 파이프 라인은 "U 파이프 라인"과 "V 파이프 라인"의 2개. 첫 번째 U 파이프가 모든 명령을 실행 가능한 메인 파이프인 반면, 두 번째 V 파이프는 단순히 명령만 실행 가능한 서브 파이프다. U 파이프와 V 파이프 동기화하여 쌍이 된 명령을 순차 실행한다. 실행 유닛도 하드 와이어드 화가 진행, 처리량이 높아졌다.

부동 소수점 연산 (FP) 유닛은, 더하기, 곱하기, 나누기의 유닛 군으로, 파이프 라인화 되어 있다. 실제로는, FP 유닛도 2 파이프를 갖추고 있지만, 두 번째 파이프는 "FXCH (floating-point exchange)"명령만 실행할 수 있다. 즉, FP 명령을 실행하는데 있어, 레지스터 스택의 가장 위만 실행 할 수 있는 x87 FP 레지스터의 제약을 회피하기 위해 FXCH 명령을 보조 실행하는 정도의 파이프다. 따라서 그림 중에서는 생략되어 있다. 또 FP 명령은 정수 연산도 쌍으로는 실행할 수 없다.

참고로, 초대 Pentium (P5)의 FP 유닛 나누기 유닛이, 후에 논란을 빚게 되는 유명한 "Pentium 나누기 버그 (Pentium FDIV Bug)"를 가졌다. Intel은 이 버그 때문에 Pentium 교환을 접수하여 방대한 지출을 쓰지만, 그 결과 Intel 사내에서의 CPU 설계의 검증 시스템이 급격히 진보했다. (빠르면 출시 2년 가까이 부터 1년 반 정도에 셈플 데모를 보이지만, 출시는 뒤인 이유 중 하나로, 이 기간동안 양산공정 확립과 양산준비및 검증. 모든 소프트웨어는 버그가 있으면 패치하면 그만이지만, 하드웨어는 바이오스 패치나, 윈도우 패치 등으로 가능한 것은 리콜 없이 해결도 되지만, 최악의 경우는 리콜을 해야 하는 차이가 있죠. 물론 이렇게 검증을 해도 사소한 버그는 어느 CPU나 다 가지고 있습니다. 펜티엄 버그는 다른 기사에 따르면 스프레드 쉬트 사용자가 평균적으로 2만 7000년에 한번 겪을 수 있는 문제로 추정한다고... 원하는 사용자는 모두 바꿔줬는데, 게임이나 워드나 하는 일반 유저들은 귀찮아서 안바꾼 사람도 꽤 많았죠.)

Pentium부터는 L1 캐시가 명령과 데이터로 분리되어, 데이터 전용 캐시로 8KB가 탑재되었다. 또 CPU 코어 외부와의 데이터 버스는 기존의 32-bit 폭에서 64 bit 폭으로 확장되었다. 파이프 라인의 구조는 5 스테이지로. 지금에 와서는 최소한의 단수지만, 당시는 표준적인 파이프 라인 단수였다. (펜티엄은 그래서 72핀(32비트) 램을 2개 달아야 작동. 486은 72핀 램을 1개만 달아도 작동. 타사 칩셋으로는 펜티엄에서도 램을 1개만 달아도 작동되게 만든 칩셋도 존재하며 약간의 성능은 저하.)

386부터 Pentium (P5)까지 파이프 라인의 변화

Intel CPU 개발의 이정표

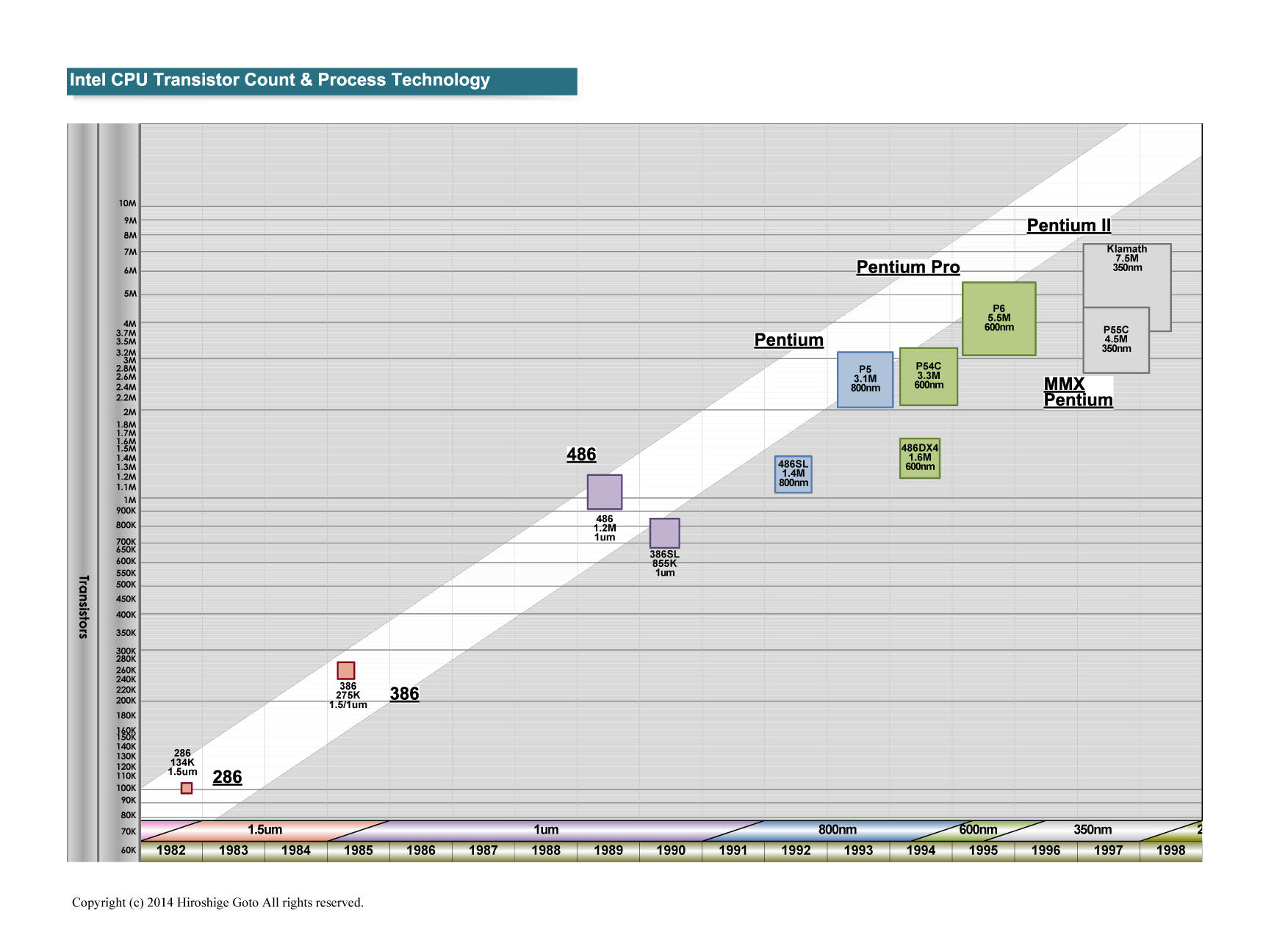

이러한 요소를 담았기 때문에 Pentium (P5)는 전 세대인 486보다 현격하게 트랜지스터 수가 많은 CPU가 되었다. 486DX가 1.2M (120만) 트랜지스터였던 것에 비해, Pentium (P5)는 3.1M (310만)으로 2배 이상 늘었다. 275K (275,000)이었던 386과 비교하면 11배의 트랜지스터 수 이다.

트랜지스터 수의 차이를 CPU의 크기로 나타낸 차트

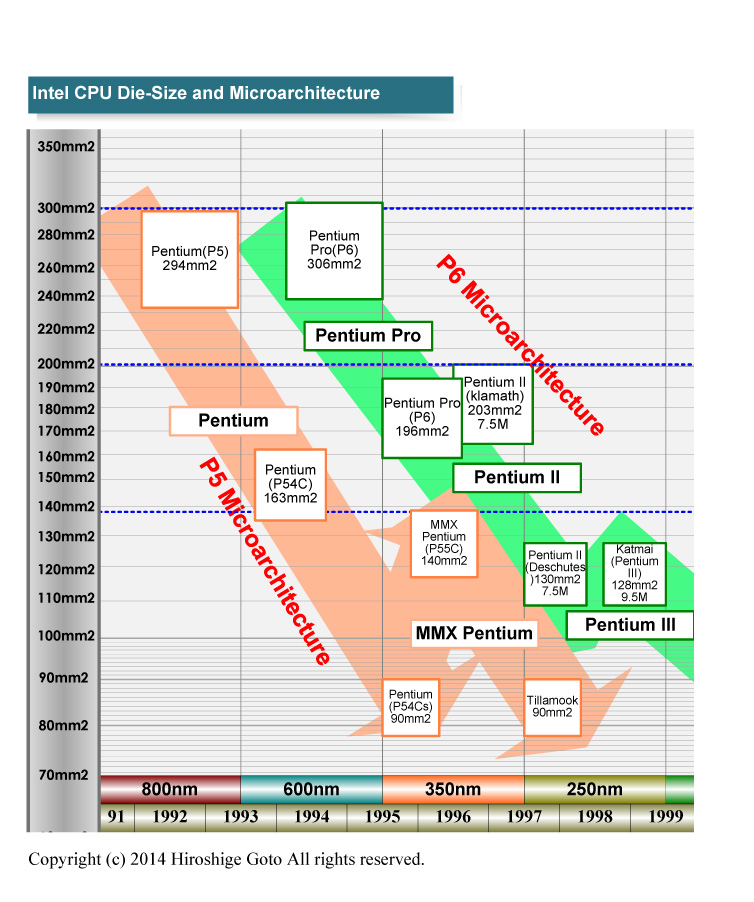

공정 기술은 0.8μm 지금 단위로 고치면 800nm. 그러나 곧 0.6μm (600nm)로 미세화 한 2 대째인 Pentium (P54C)가 등장한다. 일반 PC 사용자에게는 1994년의 Pentium (P54C)부터가 본격적인 Pentium 보급기가 된다. 동작 주파수 100 ~ 120MHz로 올라, 100MHz에 도달했다 486DX4를 넘었다. 그리고 최종적으로 0.35μm (350nm)로 축소한 Pentium (P54CS)가 등장한다. 참고로 당시 Intel의 코드 네임은 알파벳과 숫자로, P54C라면 5 아키텍처 세대, 4가 구현, C가 축소 (Compaction)를 나타낸다.

방대한 트랜지스터 수를 거두기 때문에 Pentium (P5)에서는 다이 크기도 커졌다. 초대 0.8μm 버전의 다이는 294 제곱 mm로, 당시로서는 거대 사이즈. 0.6μm의 P54C에서 163 제곱 mm로 당시의 고성능 PC용 CPU의 사이즈로, 0.35μm의 P54CS에서 메인 스트림 용 CPU인 90 제곱 mm로 축소됐다. 따라서 시장도 당초는 서버 및 워크스테이션 이었던 것이 고성능 PC, 메인 스트림 PC로 서서히 퍼져 나갔다. (예를들면 예전에는 펜티엄 CPU가 나오면 엄청나게 비싸고, 기존 486 CPU가 저렴해지면서(이쪽도 공정이전) 보급형이 되고, 더 시간이 지나면 펜티엄 CPU도 보급형까지 내려오는 패턴이 이런 이유. 지금은 그냥 처음부터 단종까지 가격이 같죠. 시장 가격이야 조금씩 다르지만.. 펜티엄의 경우 기업체나 갑부가 아닌 아주 일반 개인의 경우는 94년도 부터가 서서히 보급 되었다고 봐야겠죠. 이때도 500~600만원이 넘는 웍스테이션용 펜티엄 PC도 광고했지만, 100만원대 펜티엄 PC가 나오기 시작해, 94년 중후반 ~ 95년 초반이 펜티엄을 충분히 개인이 살 수 있을 정도가 되었다고 봐야죠. 예전 국내 뉴스를 찾아보면... 네이버 뉴스 라이브러리 용산에서 조립으로 잘 사면 이보다 좀더 싸게 샀겠죠. 물론 요즘의 100만원과 90년대 중반의 100만원은 가치가 다르기 때문에, 100만원대 펜티엄이라고 해도 개인이 살만하다는 거지, 누구나 다 펜티엄을 막 살 수 있지는 않았습니다. 컴퓨터가 꼭 필요한가 이런 문제도 있구요. 국내에서 이집저집 누구나 사고 꼭 필요하다 꼭 1대는 있어야 한다 이런 시대는 99년 ~ 2000년대 들어서죠.)

Die size 이행도

Intel CPU 전체의 트랜지스터 수의 이행을 보면, 언뜻 순조롭게 2년에서 2배 정도 트랜지스터 수가 증가해 온것 처럼 보인다. 그러나 실제로는 Intel의 로직 공정의 미세화나 다층화는, 초기에는 천천히하고, Pentium (P5)의 0.8μm (800nm) 부터 급 가속되는 것이 나타난다. 8086부터 486까지는 CPU의 다이 크기를 크게하는 것으로 트랜지스터를 늘린 측면이 있다.

또 CPU 아키텍쳐 개발도 Pentium (P5)부터 급 가속해서, 그때까지의 4년에 1 마이크로 아키텍처의 속도에서, 2년에 1 마이크로 아키텍처의 도입으로 바뀌었다. 즉, Pentium (P5)을 계기로 Intel의 논리 공정과 CPU 마이크로 아키텍처 개발은 배속화 되었다.

CPU의 트랜지스터 수의 추이

그 위에 Intel은 Pentium (P5)의 파생의 Pentium MMX부터는 명령 세트 아키텍처도 대폭 확장했다. 그때 까지는 16-bit에서 32-bit로 비트 확장은 했지만, 명령 세트의 기본은 변하지 않았다. 다른 종류의 명령 도입이라는 아키텍처면에서의 확장이 시작된 것도 넓은 의미로 Pentium 세대부터다. 이렇게 보면 Pentium이 Intel의 CPU 개발의 역사에서, 큰 이정표 였던 것을 알 수 있다.

MICROPROCESSOR REPORT

Intel Reveals Pentium Implementation Details Vol. 7, No. 4, March 29, 1993

RISC에 대한 Intel의 답변

Intel이 Pentium부터 CPU 개발에 자원을 집중하게 된 것은 치열한 경쟁에 노출되어 있었기 때문이다. Pentium이 등장한 당시, Intel은 RISC 공세 폭풍이 덮치고 있었다. CISC 계 명령어 세트는, 그 뿌리의 역사가 오래된, 핸드 코딩에 최적화 되어 있으며, 인간이 프로그램하기 쉽도록 복잡한 명령을 가진다. 명령 길이가 가변에 다양하고, 연산 명령의 오퍼랜드로 메모리를 지정할 수 있다. 이러한 CISC는 명령어 세트가 복잡해서, 명령 실행도 복잡하기 때문에 고속화를 위한 하드웨어 기술이나 컴파일러 기술의 적용이 어렵다고 했다.

반면 RISC 계 명령 세트는 처음부터 컴파일러에 최적화 되어 정의되어 있으며, 고정 명령 길이에 고정 명령 포맷. 연산의 오퍼랜드는 레지스터에 한정되어, 메모리 액세스는 로드 / 스토어 명령으로 행한다. 따라서 명령 체계는 단순해서, 명령 실행도 메모리 명령과 연산 명령이 분리되어 있기 때문에 간소해서, 따라서 고속화를 위한 하드웨어나 컴파일러 기술을 채용하기 쉽다.

이러한 명령어 세트에 대한 논의에서 RISC CPU 기반의 개인용 컴퓨터를 만들자는 기운이 높아져, MIPS나 PowerPC 기반으로 하는 PC의 계획이 일어섰다. CISC는 명령어 세트로서 이제는 임종의 때를 맞고, 이제부터는 RISC 명령 세트의 시대라는 풍조였다.

그러나 Pentium의 등장은 그러한 논의에 거의 마침표를 찍었다. 왜냐하면, CISC 명령에서도 고속화 하드웨어 기술의 적용이 가능하다고 증명했기 때문이다. CISC 계 ISA인 x86 CPU에 아직도 앞이 있다는 것을 보여, RISC로의 전환 기세를 잃게했다. 그 결과 RISC 계열의 고성능 클라이언트 CPU의 개발은 쇠퇴되어 가고 IA (x86 계)계 CPU의 독무대가되어 간다. Apple이 CISC인 모토로라 MC680x0 계에서 RISC인 PowerPC로 전환했지만 다시 CISC인 Intel CPU로 돌아온 것이 좋은 예다.

20년 후인 지금도 곳곳에 살아남은 Pentium 아키텍처

Intel은 97년에는 Pentium (P5) 아키텍처에 MMX 명령을 더한 Pentium MMX (P55C)를 추가한다. Pentium MMX (P55C)에서는 MMX 파이프를 새로 더했을 뿐만 아니라, 분기 예측의 대폭적인 강화와 캐시의 배의 용량, 명령 큐의 추가, 파이프 라인의 재검토와 파이프 라인의 6 스테이지화도 했다. 말하자면 강화판의 Pentium이다.

Pentium MMX (P55C)와 초대 Pentium (P5)의 블록 다이어그램

Pentium MMX (P55C)의 파이프 라인 구조

Pentium 마이크로 아키텍처는 지금도 곳곳에서 보게 된다. 서두에서 언급한 Larrabee와 기존의 Xeon Phi 등의 매니코어 제품이나 프로젝트는 물론, Intel의 매니코어 연구 칩이나 Near-Threshold Voltage 기술의 시험제작 칩 등, Intel의 연구 현장에서 CPU 코어의 시험 를 위해 사용하는 CPU 코어의 대부분은 Pentium 계다. 20년이 지나도 아직 Pentium은 살아있다.

Near-Threshold Voltage 기술의 시험제작 칩 "Claremont"의 P54C 코어

48 코어 연구 매니 코어 칩에 사용된 P54C 코어

Pentium 코어가 많이 쓰이는 이유는 Pentium이 작아 구현하기 쉬울 뿐만이 아닌, Pentium이 지금에 와서는 매우 밸런스가 좋은 마이크로 아키텍처이기 때문이다. 현재는 전력 효율이 최대의 과제로, 전력 효율이 높은 CPU 코어가 좋다고 생각된다. 특히 수십 개의 CPU 코어를 올리는 매니코어는 전력 효율은 매우 중요하다. 또 소비 전력을 한계까지 내린 Near-Threshold Voltage 같은 모바일용 기술에서도 CPU 코어 자체의 전력 효율이 중요하다.

인 오더 실행에 슈퍼 스칼라 Pentium은 전력 효율도 높고,

절대 성능도 적당한 위치에 있다

그리고 전력 효율은 CPU를 복잡하게 하면 할수록 떨어진다. Intel 자신의 연구에서도 아웃 오브 오더 실행이나 딥 파이프 라인으로 하면, 전력 효율이 확 떨어지는 것이 나타났다. 그러나 전력 효율을 올리려고 하면, 절대 성능이 떨어진다. 그런 의미에서 Pentium은 훌륭히 균형을 잡은 아키텍쳐가 된다. 따라서 Pentium 자체는 아니라도, 그 파생 CPU 코어는 앞으로도 여러 곳에서 쓰여 갈 것이다. Intel의 CPU 코어 중에서 가장 장수인 코어, 그것이 Pentium이다. (예전부터 RISC NT 웍스테이션 대 x86 NT 웍스테이션, NC 대 NetPC (x86) , ARM vs x86, 지금도 초 하이엔드 서버 PowerCPU vs Xeon E7 (이전은 아이테니엄이 E7의 위치), HPC는 GPU(엔비디아) vs 제온파이 등.. 마치 용의기사인 바란이 해들러? 따위는 무시하고(그덕에 해들러는 인간인 아방이 잡고) 명룡왕 벨더를 잡으러 간 느낌...-_-;;)

2014년 7월 1일 기사

1989년 3월 14일 i860 RISC 프로세서 기사

1991년 7월 22일 i860 RISC 프로세서 기사

1993년 3월 25일 i860 RISC 프로세서 기사

블로그 기타 기사는 하단의 링크 참고.

Apple WWDC 2005-The Intel Switch Revealed

Steve Jobs introduces the Mac Mini Intel

코어 솔로는 배니어스 -> 도선 -> 요나로 이어지는 펜티엄M 제품군이 요나에 와서 듀얼코어는 코어듀어, 싱글코어는 코어솔로 라는 이름을 갖게 됩니다. 콘로가 아니기 때문에 64비트는 지원하지 않습니다.

Apple WWDC 2006 Keynote - The first Mac Pro introduction

우드크레스트는 콘로 제온의 코드네임 입니다.

Windows NT on PowerPC ThinkPad

https://youtu.be/Ic0dkf1iFOY

The Computer Chronicles - PowerPC and PowerMac (1994)

The Computer Chronicles - Reduced Instruction Set Computer (RISC) (1986)

The Computer Chronicles - Intel 386 - The Fast Lane (1987)

The Computer Chronicles - Megahertz Mania (1989) (486 잠시 등장)

The Computer Chronicles - Notebook Computers (1992)

Computer Chronicles - The Intel 486 - 486 PC's (1992)

Computer Chronicles: intel i486

삭제된 바로 위 영상과 같은 영상.

The Computer Chronicles - Pentium PCs (1993)

3분 31초부터 슈퍼 스칼라 아키텍처 2 정수유닛, 2 파이프라인을 얘기하죠, 분기예측 유닛도 얘기 하구요. 11분 56초는 초기는 공정상 거대다이 고가의 펜티엄인 만큼 시스템도 초고가 시스템. 펜티엄이 대중화되는 (PC로의 가격) 때는 2~3년후. 공정진화로 대량생산. 셀러론이 나오기 전 까지는 신형 제품이 고급형, 이전 제품이 보급형으로 판매. 셀러론이 캐쉬나 또는 캐시+코어수가 적어서 다이 크기가 작기 때문에 수율이나 대량생산으로 인해서 가격이 싸듯이.. 마찬가지로 펜티엄 시절에도 최신 아키텍처 제품이 이전 제품보다 훨씬 많은 회로가 들어가기 때문에 가격이 비쌈 (게다가 신공정 개발,건설 투자비). 펜티엄 시절은 L2 캐시가 보드에 있었기 때문에 같은 아키텍처에서 L2 캐시량을 다르게 해서 크게 작게 만드는게 불가능.

The Computer Chronicles - UNIX (1985)

(도스처럼 단일 사용자용으로 만들어진 것이 아닌, 다중 사용자용으로 만들어졌기 때문에 기본적으로 멀티태스킹이 가능하죠.)

The Computer Chronicles - MS-DOS 6.2 (1993)

The Computer Chronicles - Windows NT (1993)

https://youtu.be/cHkdQ5CG0PY

(개인용은 도스+윈도 3.1 -> 윈도 95,98,Me -> XP부터 통합

서버및 웍스테이션은 윈도 NT -> 2000 -> XP부터 통합.

OS/2 에서 갈라져서 NT와 OS/2로 발전.)

Microsoft OS/2 Version 1.3 Destruction

1993 HAL-PC OS/2 NT Shootout (Uncut)

The Computer Chronicles - OS/2 (1993)

The Computer Chronicles - OS/2 Warp (1994)

https://youtu.be/mmxabyk0S2M

The Computer Chronicles - Windows 95 (1995)

후반부 21분 55초 펜티엄 프로(P6) 깨알 출현

The Computer Chronicles - Windows 98 (1998)

리누스 출연. 리누스가 자신의 인텔 386 PC에서 돌아가는 유닉스로(미닉스) 만든게 리눅스죠.

[고전 1997.09.12] 펜티엄 오버드라이브 프로세서 가격 조사

[고전 2005.11.30] 마이크로 아키텍처의 변화를 반영하는 "Core"브랜딩

[아키텍처] Core Microarchitecture 속도의 비밀은 CISC의 아름다움

[고전 2005.06.07] Mac에 Intel CPU 탑재를 잡스 CEO가 선언

[고전 1996/06/25] DOOM의 id Software에서 신작 3D 게임 "Quake" 등장

[고전 1997.10.15] Intel과 HP공동으로 "Merced"의 기초 기술을 발표 및 단신 모음

[고전 1997.10.31] Intel과 DEC 전격 제휴 MPU의 판도가 바뀐다

[고전 1998.06.10] Pentium II Xeon으로 서버 시장이 바뀐다

[고전 2000.2.25] 인텔 사내경합이 낳은 Willamette 1.4GHz

[고전 2002.10.04] Pentium 8 후보 Nehalem 아키텍처

[고전 2002.09.11] 이것이 Banias 플랫폼이다 CPU 마이크로 아키텍처 편

[고전 2004.07.21] 인텔 90nm 펜티엄 M 755 Dothan

[고전 2004.12.24] 폴락의 법칙에 찢어지고 취소된 테하스(Tejas)

[분석정보] 심플 코어로 향하는 차세대 CPU 아키텍처

[고전 2005.03.05] 2015년 컴퓨터 플랫폼 IDF Spring 2005

[분석정보] 인텔이 추진하는 32코어 CPU Larrabee

[분석정보] Larrabee에 쫓기는 NVIDIA가 GT200에게 입힌 GPGPU용 확장

[분석정보] Intel 또 하나의 차세대 CPU LPP

[분석정보] 또 하나의 초저소비 전력 CPU Silverthorne

[분석정보] 초저소비 전력을 달성한 Silverthorne의 비밀

[분석정보] Intel 48 코어 IA 프로세서를 개발

[분석정보] Intel 48코어 매니코어 연구 칩 기술 공개

[정보분석] 같은 무렵에 시작된 Nehalem과 Larrabee와 Atom

[정보분석] IDF 2011 Justin Rattner 매니코어 시대가 다가옴 2/2부

[분석정보] Research @ Intel 2012 리포트

[분석정보] Intel 매니코어 MIC 와 Atom SoC Medfield 를 발표

[분석정보] 인텔. 아톰보다 더욱 저전력 CPU Quark 발표 IDF 2013 샌프란시스코

[분석정보] 인텔 반영구적으로 자율 구동하는 무선통신 기능이 붙은 센서 단말과 초저소비 전력 x86 마이크로 콘트롤러

[분석정보] ARM버전 Windows로 시작된 x86 대 ARM의 CPU전쟁

[고전 1997.06.26] 기업의 IS부문이 주목하는 NetPC와 NC

[분석정보] 구글 크롬 OS는 왜 Network computer를 닮았나?

[분석정보] 컴퓨텍스 2013 태블릿 윈도우 라이센스 재검토 시작 윈텔(Wintel) 제국의 역습

[분석정보] TOP 500 슈퍼컴퓨터 순위 2016년 6월

[분석정보] Rev.F의 다음 다음에 오는 AMD의 차세대 코어 Hound

[고전 1997.06.26] 기업의 IS부문이 주목하는 NetPC와 NC

[분석정보] 구글 크롬 OS는 왜 Network computer를 닮았나?

[분석정보] CPU 고속화의 기본 수단 파이프라인 처리의 기본 1/2

[분석정보] CPU 고속화의 기본 수단 파이프라인 처리의 기본 2/2

[분석정보] 슈퍼 스칼라에 의한 고속화와 x86의 문제점은

[분석정보] 명령의 실행 순서를 바꿔 고속화 하는 아웃 오브 오더

[분석정보] x86을 고속화하는 조커기술 명령변환 구조

'벤치리뷰·뉴스·정보 > 아키텍처·정보분석' 카테고리의 다른 글

| [분석정보] 저가 IA 안드로이드가 태블릿 시장을 바꾼다 (0) | 2014.07.31 |

|---|---|

| [분석정보] ARM 코어와 x86 코어를 동등하게 다루는 AMD의 CPU 전략 (0) | 2014.07.30 |

| [벤치리뷰] AMD 멘틀 API 테스트 (0) | 2014.07.16 |

| [분석정보] ARM 코어의 다양한 라이센스 모델과 CPU코어의 설계 흐름 (0) | 2014.07.10 |

| [분석정보] PC 세계 점유율 No.1 Lenovo가 여전히 성장할 수 있는 이유는? (0) | 2014.06.24 |

| [분석정보] TOP500 슈퍼컴퓨터 순위 2014년 06월 (0) | 2014.06.23 |

| [분석정보] 컴퓨텍스 2014 인텔 저전력 모바일 Broadwell은 Core M 브랜드 (0) | 2014.06.03 |

| [분석정보] 0달러 Windows와 Bay Trail-Entry가 열어가는 저가 태블릿 시장 (0) | 2014.04.25 |